# **Comparison Between GR716A and GR716B**

Application Note 2023-05-24

Doc. No GR716B-COMP-1

Issue 1.1

Doc. No:

GR716B-COMP-1

Issue:

1

Rev.:

1

Date:

2023-05-24

Page:

2 of 8

Status:

Approved

#### **CHANGE RECORD**

| Issue | Date       | Section / Page | Description                                                                                      |

|-------|------------|----------------|--------------------------------------------------------------------------------------------------|

| 1.0   | 2022-04-11 |                | First release                                                                                    |

| 1.1   | 2023-05-24 |                | Clarified precision voltage reference. Updated various fields in comparison table in section 2.2 |

#### TABLE OF CONTENTS

| 1 | Intr | oduction                     | . 2 |

|---|------|------------------------------|-----|

|   |      | Scope of the Document        |     |

|   |      | Reference Documents          |     |

|   |      | erview                       |     |

|   |      | Overview                     |     |

|   | 2.2  | Comparison                   | . 5 |

|   |      | Changes in memory map        |     |

|   |      | Changes of package body size |     |

#### 1 INTRODUCTION

## 1.1 Scope of the Document

This document presents the differences between Frontgrade Gaisler's revised GR716B design versus the already existing GR716A device.

The GR716B microcontroller has been developed in an activity with support from the European Space Agency under ARTES Competitiveness & Growth programme. The purpose of the work was to develop a new generation microcontroller, GR716B, based on the GR716A microcontroller.

#### 1.2 Reference Documents

The following documents are referred as they contain relevant information:

| [RD1] | GR716A Datasheet and User's manual, Version 3.2 |

|-------|-------------------------------------------------|

|       |                                                 |

[RD2] GR716B Advanced Datasheet and User's manual, Version 0.5

[RD3] LEON-REX Instruction Set Extension, Frontgrade Gaisler

Doc. No:

GR716B-COMP-1

Issue:

1

Rev.:

1

Date:

2023-05-24

Page:

3 of 8

Status:

Approved

#### 2 OVERVIEW

#### 2.1 Overview

The GR716B microcontroller has been developed in an activity with support from the European Space Agency under ARTES Competitiveness & Growth programme. The purpose of this activity was to develop an improved microcontroller, GR716B, based on the GR716A microcontroller and to enrich the software ecosystem by industrialization of state-of-the art operating systems, development and simulation tools

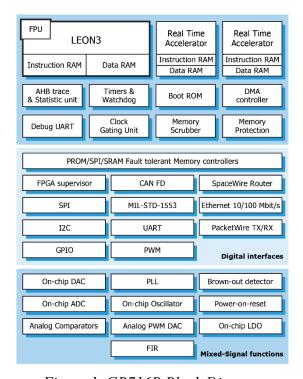

Figure 1 GR716B Block Diagram

The GR716B microcontroller is a single core LEON3FT SPARC V8 processor, with advanced interface protocols, that has been optimized for real-time systems and deterministic software execution. Features such as SPARC V8E Alternate Window Pointer, interrupt zero jitter latency, SPARC V8E multiply step instructions and the possibility to run software (including interrupt handlers) from local RAM are supported to increase the determinism and responsiveness in the system. The LEON-REX instruction set extension is also supported by the microcontroller and is further described in [RD3]. The GR716B implements also two Real Time Accelerators (RTA) whose purpose is to offload the main LEON3 for simple tasks.

The GR716B architecture is centred around multiple instances of the AMBA Advanced High-speed Bus (AHB), to which the LEON3FT processor and other high-bandwidth units are connected. Low bandwidth peripherals/functions are connected to the AMBA Advanced Peripheral Bus (APB) which is accessed through an AHB to APB bridge. The use of multiple processor buses also enables non-intrusive debugging and the possibility to have direct access to on-board memory without interrupting or involving the LEON3FT processor. 64 external CMOS pins and 8 LVDS transceivers are configurable from software via configuration registers. Pre-defined pin configurations are defined in the boot software and can be enabled by using pull-up/pull-down resistors on external pins during reset. A pre-defined configuration of external pins is useful in cases when the microcontroller should

Doc. No:

GR716B-COMP-1

Issue:

1

Rev.:

1

Date:

2023-05-24

Page:

4 of 8

Status:

Approved

boot from external memories or remote controlled via SpaceWire, CAN FD, UART and SPI after reset. The program controlling the microcontroller needs to set appropriate direction and functionality on all pins after reset depending on the environment that the microcontroller is used in. On-chip LVDS transceivers with support for common-mode, cold-spare and fail-safe for SpaceWire and SPI for Space as well as dedicated pins for external SPI boot ROM boot are available and can optionally be used.

The microcontroller has a high level of integrated analogue functions:

- Analogue to Digital Converters (ADC)

- Brown out detection

- Crystal Oscillator

- Digital to Analogue Converters (DAC)

- Analogue Comparators

- Power-on and reset functionality

- and Linear Voltage Regulators for single 3.3V supply.

Doc. No:

GR716B-COMP-1

Issue:

1

Rev.:

1

Date:

2023-05-24

Page:

5 of 8

Status:

Approved

# 2.2 Comparison

The table below compares GR716A [RD1] and GR716B [RD2]. Differences have been marked in bold text.

| Feature                              | GR716A                                                                                                           | GR716B                                                                                                                                                                                                      |  |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Availability and Qualification state | Screening tests as per ESCC9000.<br>Lot Qualification as per ESCC2567000/ESCC9000                                | Screening and Lot Qualification as per ESCC9000.                                                                                                                                                            |  |  |  |

| Device ID                            | 0x0716 / 4204                                                                                                    | 0x0716 / xxxx (TBC)                                                                                                                                                                                         |  |  |  |

| Package                              | CQFP132                                                                                                          | CQFP132                                                                                                                                                                                                     |  |  |  |

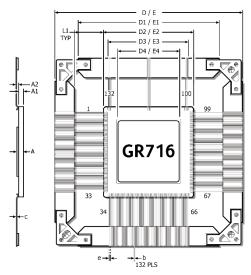

| Package Dimension                    |                                                                                                                  | D2/E2 dimension is increased by 1.1 mm in the GR716B. See chapter 2.4 for more information                                                                                                                  |  |  |  |

| Power                                | < 200mW @ ambient room temperature<br>< 825mW @ 110°C max power use case                                         | < 250mW@ ambient room temperature<br>< 1000mW @ 125°C max power use case                                                                                                                                    |  |  |  |

| Supply Voltage                       | +3V3                                                                                                             | +3V3                                                                                                                                                                                                        |  |  |  |

| Temperature range                    | -55°C to +110°C                                                                                                  | -55°C to +125°C                                                                                                                                                                                             |  |  |  |

| Radiation-tolerant                   | Yes                                                                                                              | Yes                                                                                                                                                                                                         |  |  |  |

| User Package Pins                    | Dedicated SPI memory interface 64 CMOS GPIOs with programmable pull-up / pull-down resistors 6 LVDS transceivers | Dedicated SPI memory interface 64 CMOS GPIOs with programmable pull- up / pull-down resistors, and Schmitt trigger inputs. 8 LVDS transceivers with cold-spare, fail-safe and extended common mode support. |  |  |  |

| Max system frequency                 | 50MHz                                                                                                            | 100MHz                                                                                                                                                                                                      |  |  |  |

| Performance                          | >70 DMIPS                                                                                                        | Main CPU >140 DMIPS<br>RTA 0 >140 DMIPS<br>RTA 1 >140 DMIPS                                                                                                                                                 |  |  |  |

| FPU                                  | Supported                                                                                                        | Supported by main CPU                                                                                                                                                                                       |  |  |  |

| Real Time Accelerator                | n/a                                                                                                              | Programmable Real-Time-Accelerators (RTA) improves the overall performance by a factor of 3.                                                                                                                |  |  |  |

| Internal memory                      | 192KiB                                                                                                           | 192KiB                                                                                                                                                                                                      |  |  |  |

| External memory interface            | SPI, FLASH/SRAM, I2C                                                                                             | SPI, FLASH/SRAM, I2C                                                                                                                                                                                        |  |  |  |

| Debug Interface                      | 2 port UART                                                                                                      | 2 port UART                                                                                                                                                                                                 |  |  |  |

| Remote access interface              | SpaceWire, UART, SPI, I2C                                                                                        | SpaceWire, CAN FD, UART, SPI, I2C                                                                                                                                                                           |  |  |  |

| Boot memory                          | SPI, FLASH/SRAM, I2C                                                                                             | SPI, FLASH/SRAM                                                                                                                                                                                             |  |  |  |

| SpaceWire                            | SpaceWire interface                                                                                              | SpaceWire Router with 2 external ports                                                                                                                                                                      |  |  |  |

| CAN                                  | CAN 2.0                                                                                                          | CAN FD with CANOpen support                                                                                                                                                                                 |  |  |  |

| MIL-STD-1553B                        | Supported                                                                                                        | Supported                                                                                                                                                                                                   |  |  |  |

| Ethernet                             | n/a                                                                                                              | 10/100Mbit                                                                                                                                                                                                  |  |  |  |

Doc. No:

GR716B-COMP-1

Issue:

1

Rev.:

1

Date:

2023-05-24

Page:

6 of 8

Status:

Approved

| FPGA supervisor for programming and scrubbing configuration memory | n/a                                                                                                          | Support for Xilinx Virtex5 and Xilinx Kintex Ultra Scale FPGA                                                                   |  |  |  |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Misc Peripherals                                                   | UART, SPI, SPI For Space, I2C                                                                                | UART, SPI, SPI For Space, I2C                                                                                                   |  |  |  |

| PWM                                                                | Programmable PWM interface                                                                                   | Programmable PWM, including unique configurations for switching-power and motor-control applications.                           |  |  |  |

| DAC 12bit @ 3Msps, 4 channels                                      |                                                                                                              | 12bit @ 3Msps, 4 channels<br>PWM DAC 24bit, 25MSps, 8 channels                                                                  |  |  |  |

| ADC Two ADC 11bits @ 200Ksps, 4 differential or 8 single ended     |                                                                                                              | Four ADC 11bits/14bits @ 500Ksps, 8 differential or 16 single ended                                                             |  |  |  |

| External voltage reference                                         | 2.4V, maximum load current 2mA                                                                               | 1.9V, maximum load current 20mA                                                                                                 |  |  |  |

| Analog comparators                                                 | n/a                                                                                                          | 20 channels, 25ns, 7 programmable internal comparison levels or external connection.                                            |  |  |  |

| FIR Filter                                                         | n/a                                                                                                          | 8 channels, 25MSps, 27 binary programmable taps, configurable from analog comparator etc, e.g. latch-up detection applications. |  |  |  |

| DMA                                                                | Programmable DMA channels                                                                                    | Programmable DMA channels with support for 'if-else' statements                                                                 |  |  |  |

| Analog on chip support                                             | Power-on-Reset, Oscillator, Brown-out detection, LVDS transceivers, regulators to support single 3.3V supply | Power-on-Reset, Oscillator, Brown-out detection, LVDS transceivers, regulators to support single 3.3V supply                    |  |  |  |

## 2.3 Changes in memory map

- General purpose register bank: The address map has been changed between the GR716A and GR716B. The functionality driven by the registers can be different between the devices due to more configurability in the GR716B device

- Analog register configuration: Address map and functionality has changed between the GR716A and GR716B

- New functionality: Configuration registers has been added for new interfaces and functions

- Support for external ADC/DAC interface has been removed

Doc. No:

GR716B-COMP-1

Issue:

1

Rev.:

1

Date:

2023-05-24

Page:

7 of 8

Status:

Approved

# 2.4 Changes of package body size

Three of the package parameters have been changed to allow new functionalities in the GR716B. Changed parameters are marked with bold text in the table below.

| Name     | Parameter                                       | GR716A      |       |              | GR716B |       |       |

|----------|-------------------------------------------------|-------------|-------|--------------|--------|-------|-------|

|          |                                                 | Min         | Тур   | Max          | Min    | Тур   | Max   |

| A        |                                                 |             | 3.05  | 3.5          |        | 3.05  | 3.5   |

| A1       |                                                 |             |       | 2.26         |        |       | 2.26  |

| A2       |                                                 |             |       | 0.53         |        |       | 0.53  |

| b1       | Width of lead when closest to case              | 0.23        |       | 0.329        | 0.23   |       | 0.329 |

| b2       | Width of lead when closest to ceramic bar       | 0.15        |       | 0.25         | 0.15   |       | 0.25  |

| c        |                                                 | 0.075       |       | 0.175        | 0.075  |       | 0.175 |

| D/E      |                                                 |             | 50.85 |              |        | 50.85 |       |

| D1/E1    |                                                 |             | 30.73 |              |        | 30.73 |       |

| D2/E2 1) |                                                 | 23.88       |       | 24.26        | 25.1   |       | 25.48 |

| D3/E3    |                                                 |             | 20.32 |              |        | 20.32 |       |

| D4/E4    |                                                 |             | 20.2  |              |        | 22.0  |       |

| e        |                                                 |             | 0.635 |              |        | 0.635 |       |

| L1 1)    | Length of lead from case to ceramic bar (L2+L3) |             | 8.3   |              |        | 7.75  |       |

| L2 1)    | Length of lead with width b1                    |             | 7.0   |              |        | 6.45  |       |

| L3       | Length of lead with width b2                    |             | 1.3   |              |        | 1.3   |       |

| Mass     | Mass of case, including the lead frames.        | 8.5±1 grams |       | 8.5±1 grams. |        |       |       |

Note 1 Dimension D2/E2 for GR716B is increased by 1.1 mm. To prepare PCB footprint for replacement, it is suggested to adjust the solder pad length accordingly. Dimension L1 and L2 will at the same time be reduced with by up to 0.55 mm.

Doc. No:

GR716B-COMP-1

Issue:

1

Rev.:

1

Date:

2023-05-24

Page:

8 of 8

Status:

Approved

Frontgrade Gaisler AB reserves the right to make changes to any products and services described herein at any time without notice. Consult the company or an authorized sales representative to verify that the information in this document is current before using this product. The company does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by the company; nor does the purchase, lease, or use of a product or service from the company convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual rights of the company or of third parties. All information is provided as is. There is no warranty that it is correct or suitable for any purpose, neither implicit nor explicit.

Copyright © 2023 Frontgrade Gaisler AB