# CRES PIONEERING ADVANCED FLECTRONICS

### **Features**

- Fault tolerant 18x SpaceWire Router compatible with ECSS-E-ST-50-12C

- Supports ECSS-E-ST-50-12C Rev 1 features

- Non-blocking switch-matrix connecting any input port to any output port

- Packet Distribution, Group Adaptive Routing

- Path, Logical and Regional Logical addressing

- Two priority levels for output port arbitration

- 16x SpaceWire ports with on-chip LVDS

- 2x SpaceWire ports with LVTTL

- Configuration port using RMAP, compliant with ECSS-E-ST-50-52C

- Support functions for SpaceWire-D

- Distributed Interrupt support

- System-time distribution via all ports

- SpaceWire Plug-and-Play support

- Timers on all ports to recover from deadlock

- UART and JTAG interfaces to configuration port

- GPIO and SPI interfaces

- Do not fully support failsafe operation of LVDS as defined by ECSS-E-ST-50-12C

- Does not support cold sparing

### **Description**

The Radiation-Tolerant 18x SpaceWire Router device is ideally suited for space and other high-rel applications, providing a high-throughput wormhole router functionality.

### **Specification**

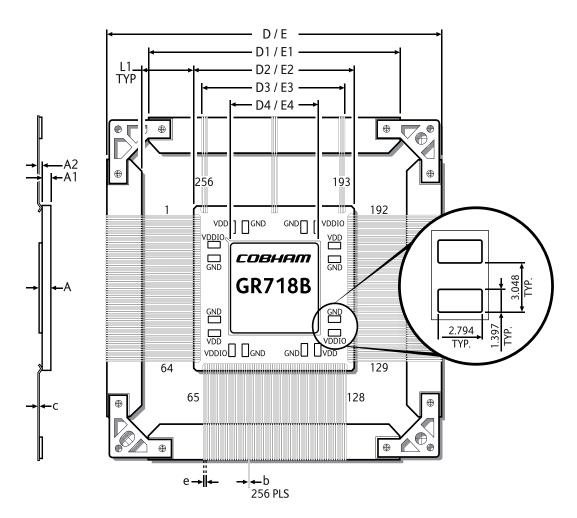

- CQFP256 hermetically sealed ceramic package

- Total Ionizing Dose (TID) up to 300 krad (Si)

- Single-Event Latch-Up Immunity (SEL) to LET<sub>TH</sub> > 118 MeV-cm<sup>2</sup> mg

- Single-Event Upset (SEU) below 10<sup>-12</sup> bit error rate in space environment

- 1.8 V and 3.3 V supply

- 2.8 W consumption (typical)

- Up to 200 Mbps on all SpaceWire links

### **Applications**

The router implements a routing switch as defined in the ECSS-E-ST-50-12C SpaceWire links, nodes, routers and networks standard, supporting all mandatory and optional features.

The router implements eighteen external routing ports, an internal configuration port, and an internal port for system level test support.

The configuration port provides access to configuration and status registers, and the routing table, using the Remote Memory Access Protocol (RMAP) as defined in the ECSS-E-ST-50-52C protocol standard.

The router also fully supports the ECSS-E-ST-50-51C SpaceWire protocol identification standard.

## **Table of contents**

| 1  | Introduction                  |                                |    |  |  |

|----|-------------------------------|--------------------------------|----|--|--|

|    | 1.1                           | Scope                          | 4  |  |  |

|    | 1.2                           | Reference documents            | 4  |  |  |

|    | 1.3                           | Document revision history      | 5  |  |  |

|    | 1.4                           | Acronyms                       | 10 |  |  |

|    | 1.5                           | SpaceWire routing introduction | 11 |  |  |

|    | 1.6                           | Errata                         | 12 |  |  |

| 2  | Architecture                  |                                |    |  |  |

|    | 2.1                           | Overview                       | 13 |  |  |

|    | 2.2                           | Cores                          | 15 |  |  |

|    | 2.3                           | Memory map                     | 16 |  |  |

|    | 2.4                           | Register overview              | 18 |  |  |

| 3  | I/O I                         | Pins                           | 22 |  |  |

| 4  | Cloc                          | ks and reset                   | 24 |  |  |

|    | 4.1                           | Clocks                         | 24 |  |  |

|    | 4.2                           | Reset                          | 25 |  |  |

| 5  | GPIC                          | O pin multiplexing             | 26 |  |  |

| 6  | Spac                          | eWire Router                   | 32 |  |  |

|    | 6.1                           | Overview                       |    |  |  |

|    | 6.2                           | Operation                      |    |  |  |

|    | 6.3                           | SpaceWire ports                | 43 |  |  |

|    | 6.4                           | SIST port                      | 44 |  |  |

|    | 6.5                           | Configuration port             | 44 |  |  |

| 7  | Spac                          | eWire In-System Test           | 73 |  |  |

|    | 7.1                           | Overview                       | 73 |  |  |

|    | 7.2                           | Operation                      | 73 |  |  |

|    | 7.3                           | Registers                      | 75 |  |  |

| 8  | UAR                           | RT Interface                   | 85 |  |  |

|    | 8.1                           | Overview                       | 85 |  |  |

|    | 8.2                           | Operation                      | 85 |  |  |

|    | 8.3                           | Registers                      | 86 |  |  |

| 9  | JTAG Interface                |                                |    |  |  |

|    | 9.1                           | Overview                       | 88 |  |  |

|    | 9.2                           | Operation                      | 88 |  |  |

| 10 | SPI (                         | Controller                     | 89 |  |  |

|    | 10.1                          | Overview                       | 89 |  |  |

|    | 10.2                          | Operation                      | 89 |  |  |

|    | 10.3                          | Registers                      | 91 |  |  |

| 11 | General Purpose I/O Interface |                                |    |  |  |

|    | 11.1                          | Operation                      | 96 |  |  |

|    | 11.2                          | Registers                      | 96 |  |  |

| 12 | Syste                         | em Level Test Configuration    | 98 |  |  |

|    | 12.1                          | Registers                      | 98 |  |  |

| 13 | AME                    | 99                                                 |     |

|----|------------------------|----------------------------------------------------|-----|

|    | 13.1                   | Overview                                           |     |

|    | 13.2                   | Operation                                          |     |

| 14 | AME                    | 100                                                |     |

|    | 14.1                   | Overview                                           | 100 |

|    | 14.2                   | Operation                                          | 100 |

| 15 | Electrical description |                                                    |     |

|    | 15.1                   | Absolute maximum ratings                           | 101 |

|    | 15.2                   | Recommended operating conditions                   | 102 |

|    | 15.3                   | Power supplies                                     | 103 |

|    | 15.4                   | Input voltages, leakage currents and capacitances  | 104 |

|    | 15.5                   | Output voltages, leakage currents and capacitances | 105 |

|    | 15.6                   | Simplified IO buffer schematics                    | 107 |

|    | 15.7                   | AC characteristics                                 | 108 |

| 16 | Mech                   | hanical description                                | 116 |

|    | 16.1                   | Component and package                              | 116 |

|    | 16.2                   | Pin assignment                                     |     |

|    | 16.3                   | Mechanical package drawings                        | 123 |

| 17 | Ordering information   |                                                    | 124 |

# 1 Introduction

# 1.1 Scope

This document is the data sheet and user's manual for revision B of the GR718 - Radiation Tolerant 18x SpaceWire Router. The GR718 was developed in an activity initiated by the European Space Agency under ESTEC contract 4000105402/12/NL/CBi.

## 1.2 Reference documents

[SPWINT]

| [AMBA]   | AMBA <sup>TM</sup> Specification, Rev 2.0, ARM IHI 0011A, 13 May 1999, Issue A, first release, ARM Limited                               |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| [SPW]    | ECSS - Space Engineering, SpaceWire - Links, nodes, routers and networks, ECSS-E-ST-50-12C, July 2008                                    |

| [SPWID]  | ECSS - Space Engineering, SpaceWire protocol identification, ECSS-E-ST-50-51C, February 2010                                             |

| [RMAP]   | ECSS - Space Engineering, SpaceWire - Remote memory access protocol, ECSS-E-ST-50-52C, February 2010                                     |

| [SPWPNP] | ECSS - Space Engineering, SpaceWire Plug-and-Play protocol, ECSS-E-ST-50-54C Draft, March 2013                                           |

| [SPWD]   | SpaceWire-D - Deterministic Control and Data Delivery over SpaceWire Networks, Draft B, April 2010, ESA Contract Number 220774-07-NL/LvH |

SpaceWire Conference, Nara, November 2008 (outdated)

Yuriy Sheynin, Distributed Interrupts in SpaceWire Interconnections, International

# 1.3 Document revision history

Change record information is provided in table 1.

Table 1. Change record

| Version | Date           | Sections | Note                                                                                                                                                 |

|---------|----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.5     | 2013 September | All      | Document updated after tape-out. All sections affected.                                                                                              |

| 1.6     | 2013 October   | All      | Created new section 1, and moved Reference documents and Document revision history to section 1. Old section 1 was split into section 2, 3, 4, 5.    |

|         |                |          | Moved section 2.8 to section 6.2.20                                                                                                                  |

|         |                |          | Moved section 2.9 to section 6.2.22                                                                                                                  |

|         |                |          | Changed name of SPW_CLK pin to SPWCLK.                                                                                                               |

|         |                |          | Added complete register overview with acronyms for all registers.                                                                                    |

|         |                |          | Changed name of section General Purpose Register to System Level Test Configuration. Moved description of loop-back to this section.                 |

|         |                |          | Updated block diagram (figure 1).                                                                                                                    |

|         |                |          | Added acronyms for UART, SPI, GPIO, and GPREG registers to respective section's register table, as well as both AMBA and RMAP address.               |

|         |                |          | Clarified the memory map and AMBA plug & play                                                                                                        |

|         |                |          | Added reset value column to I/O pins (table 12).                                                                                                     |

|         |                |          | Changed complete GPIO pin multiplexing section to make it clearer.                                                                                   |

|         |                |          | Rewrote Interrupt distribution subsection (in SpaceWire router section). Now named Distributed interrupt support, and includes more details.         |

|         |                |          | Added SpaceWire routing introduction to section 1.5.                                                                                                 |

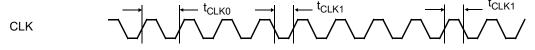

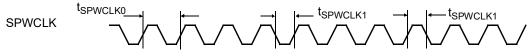

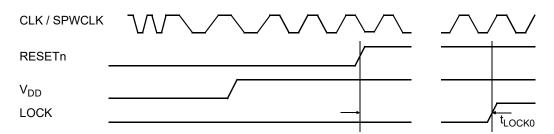

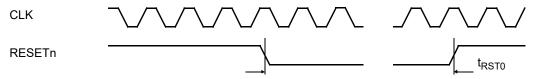

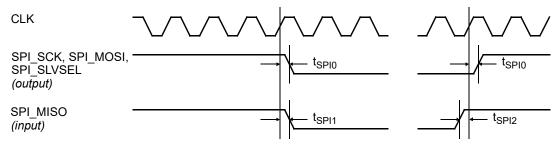

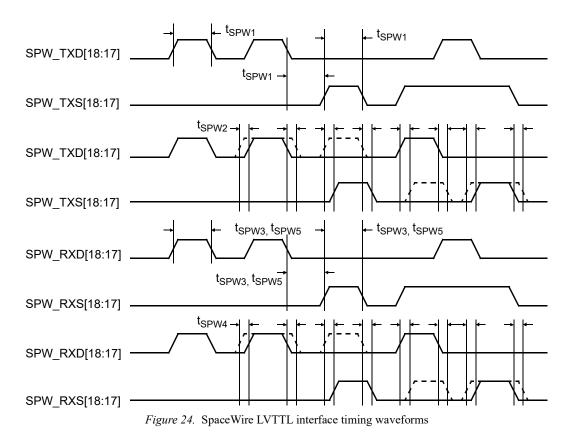

|         |                |          | Added timing diagram for LOCK pin to AC characteristics section, as well as various fixes to other timing diagrams in order to make them more clear. |

|         |                |          | SPW_RXSn and SPW_TXSn were mapped to the wrong pins in the pin list.                                                                                 |

|         |                |          | Changed so that all registers use the same layout. Added register layout example to the Register overview section.                                   |

|         |                |          | Fixed various spelling errors throughout the document.                                                                                               |

|         |                |          | Minor clarifications throughout the document.                                                                                                        |

Table 1. Change record

| Version | Date          | Sections | Note                                                                                                                                          |

|---------|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1.7     | 2014 February | All      | Changed affix for package from -CG256 to -CQ256.                                                                                              |

|         |               |          | Register description for Port status register (table 28) showed wrong bit index for PB and PR fields. Also, description for RE bit was wrong. |

|         |               |          | SpW PnP address range in table 6 was defined as 0x0000-0x8001. Changed to 0x000000000-0x0000C000.                                             |

|         |               |          | Changed RMAP addresses in register tables from 0xNNNN to 0xNNNNNNN format.                                                                    |

|         |               |          | Moved static routing section to 6.2.6                                                                                                         |

|         |               |          | Changed layout of overview table for SpaceWire Plug-and-Play registers.                                                                       |

|         |               |          | Replaced "packet timer" with "data character timer" in order to have a name that better describes the use of the timer.                       |

|         |               |          | Clarified how link-rate is set by adding a formula.                                                                                           |

|         |               |          | Clarified how the RMAP target handles write commands larger than four bytes (i.e. to more than one register)                                  |

|         |               |          | Clarified group adaptive routing and packet distribution.                                                                                     |

|         |               |          | Fixed error claiming that RMAP commands denied access due to the access control features described in 6.5.1.3 were "silently discarded".      |

|         |               |          | Moved section about packet length truncation from subsection of SpaceWire-D to its own section, because it's not really part of SpaceWire-D.  |

|         |               |          | Added more details about AMBA plug & play in order to remove reference to GRLIB.                                                              |

|         |               |          | Changed layout for description of SIST register fields to match all other registers.                                                          |

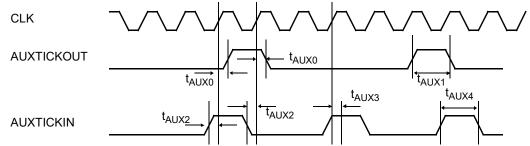

|         |               |          | Clarified timing diagram for AUXTICKIN and AUXTICK-OUT signals.                                                                               |

|         |               |          | Updated electrical parameters.                                                                                                                |

|         |               |          | Updated pin placement.                                                                                                                        |

|         |               |          | Fixed various spelling errors throughout the document.                                                                                        |

|         |               |          | Minor clarifications throughout the document.                                                                                                 |

Table 1. Change record

| Version | Date       | Sections                                                                    | Note                                                                                                                                                                                                                                                                                                             |

|---------|------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.8     | 2015 March | 2.4, 6.5.3                                                                  | Wrong start address for SpaceWire router's Credit counter registers (RTR.CREDCNT)                                                                                                                                                                                                                                |

|         |            | 6.5.3, 6.2.16                                                               | Register bit RTR.RTRCFG.IP (bit 11) had wrong acronym in table overview (SD instead of IP). Changed acronym for bits 9 and 10 in RTR.RTRCFG register from TA and IA to AT and AI respectively, due to conflict with other acronyms.                                                                              |

|         |            | 2.4                                                                         | Wrong start address for SpaceWire router's port control registers (RTR.PCTRL)                                                                                                                                                                                                                                    |

|         |            | 7.3                                                                         | Wrong name for register in table 92 (SIST.CTRL register)                                                                                                                                                                                                                                                         |

|         |            | 6.3.2                                                                       | Clarified that link is allowed to enter the started state if link-start-on-request is trying to start the port.                                                                                                                                                                                                  |

|         |            | 6.5.3, 6.2.10                                                               | Changed acronym for bit 18 in RTR.PCTRL register from LS to LR due to conflict with other acronym.                                                                                                                                                                                                               |

|         |            | 15.1                                                                        | Added note about common ground                                                                                                                                                                                                                                                                                   |

|         |            | 15.3                                                                        | Added Core Standby Current                                                                                                                                                                                                                                                                                       |

|         |            | 15.4, 15.5                                                                  | Corrected unit for parameters.                                                                                                                                                                                                                                                                                   |

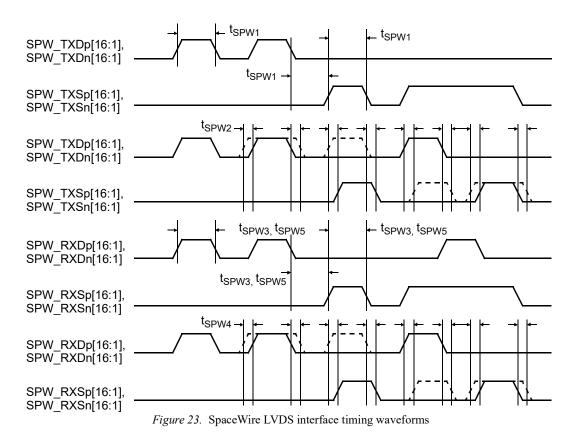

|         |            | 15.6.6, 15.6.7                                                              | Updated data and strobe input skew, jitter and hold                                                                                                                                                                                                                                                              |

|         |            | 16.2                                                                        | Merged ground and supply pin groups                                                                                                                                                                                                                                                                              |

| 2.0     | 2015 June  | Throughout doc<br>(no change bars)                                          | Changed wording to conform with upcoming revision 1 of the SpaceWire standard: interrupt-code changed to interrupt code; interrupt-acknowledge-code changed to interrupt acknowledgement code; distributed interrupt code used when talking about either an interrupt code or an interrupt acknowledgement code. |

|         |            | 5 (table 14 to 20), 6.2.16, 6.5.3 (table 32), 15.6.11                       | Added possibility to have auxiliary time-code / distributed interrupt code interface inputs to be asynchronous to CLK.                                                                                                                                                                                           |

|         |            | 5 (table 20)                                                                | Changed time-code / distributed interrupt code reset configuration.                                                                                                                                                                                                                                              |

|         |            | 6.5.3 (table 34),<br>6.5.4 (table 66)                                       | Changed minor version number to 3.                                                                                                                                                                                                                                                                               |

|         |            | 6.5.3 (table 46)                                                            | Changed ISR change timers to 10 bits.                                                                                                                                                                                                                                                                            |

|         |            | 6.5.3 (table 23)                                                            | Changed description of routing table port map registers, since they now read zero after reset for logical addresses.                                                                                                                                                                                             |

|         |            | 2.4 (table 8),                                                              | Added support for distributed interrupts to operate in extended                                                                                                                                                                                                                                                  |

|         |            | 5 (table 20),<br>6.2.15, 6.5.3<br>(tables 22, 31,<br>32, 41, 42, 43,<br>44) | interrupt mode, i.e with 64 interrupt codes instead of 32 interrupt codes + 32 interrupt acknowledgement codes.                                                                                                                                                                                                  |

|         |            | 6.5.3 (table 41)                                                            | Fixed error in description of RTR.ICODEGEN.UA bit. Functionality does not depend on RTR.ICODEGEN.AH bit.                                                                                                                                                                                                         |

|         |            | Throughout doc                                                              | Renamed device to GR718B                                                                                                                                                                                                                                                                                         |

Table 1. Change record

| Version | Date          | Sections                                                                                                                                  | Note                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1     | 2015 October  | 16.2 (Table 149)                                                                                                                          | Corrected the direction for LVDS reference pins                                                                                                                                                                                                                                                                                                                                                            |

|         |               | 16.2 (Table 149)                                                                                                                          | Modified recommendation for decoupling of analog PLL supply                                                                                                                                                                                                                                                                                                                                                |

|         |               | 15.2 (Table 132)                                                                                                                          | Note for recommended operating conditions for V <sub>DDIO</sub>                                                                                                                                                                                                                                                                                                                                            |

|         |               | 15.1 (Table 131)                                                                                                                          | Absolute maximum values for maximum voltage                                                                                                                                                                                                                                                                                                                                                                |

|         |               | 15.1 (Table 131)                                                                                                                          | Absolute maximum values for Analog PLL supply                                                                                                                                                                                                                                                                                                                                                              |

|         |               | 15.2 (Table 132)                                                                                                                          | Recommended values for Analog PLL supply                                                                                                                                                                                                                                                                                                                                                                   |

|         |               | 15.3 (Table 133)                                                                                                                          | PLL supply current                                                                                                                                                                                                                                                                                                                                                                                         |

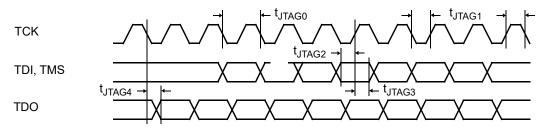

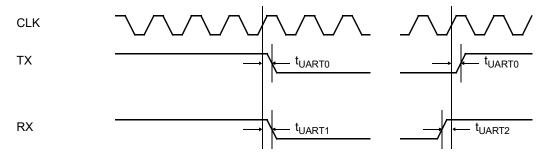

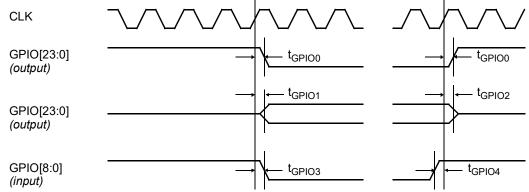

|         |               | 15.6.5 (Table<br>142), 15.6.8<br>(Table 145),<br>15.6.9 (Table<br>146), 15.6.11<br>(Table 148)                                            | Updated timing parameters for JTAG, SPI, GPIO and AUX                                                                                                                                                                                                                                                                                                                                                      |

|         |               | 16.2 (Table 149)                                                                                                                          | Pin description and direction of LVDSREF[0] and LVDS-REF[2] are updated.                                                                                                                                                                                                                                                                                                                                   |

| 2.2     | 2015 November | All                                                                                                                                       | Updated page layout, no changes to the contents.                                                                                                                                                                                                                                                                                                                                                           |

| 2.3     | 2016 April    | 15.1, 15.2, 15.3,<br>15.4, 15.6, 16,<br>16.3                                                                                              | Updated absolute maximum rating and recommended conditions.  Updated power supply condition and ratings Updated input/output DC characteristics Added equivalent load model for AC test Updated AC parameters Changed names on LVDSREF[0] pin to SELVREF and LVDS-REF[2] to VREFEXT, LVDSREF[1] to LVDSREF Updated tolerance on resistance for external LVDS reference Added mechanical drawing of package |

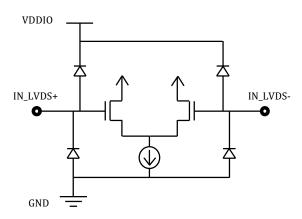

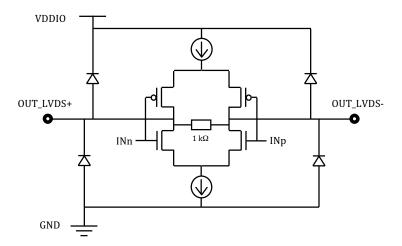

| 2.4     | 2016 November | 2.1, 3 (Table<br>12), 15.1 (Table<br>133), 15.2<br>(Table 134),<br>15.4 (Table<br>137), 15.5<br>(Table 139),<br>15.6, 16.2<br>(Table 151) | Clarification of LVDS properties. Added LVDS input and output simplified buffer schematics.                                                                                                                                                                                                                                                                                                                |

| 2.5     | 2017 January  | 16.2 (Table 151)                                                                                                                          | Clarification of tolerance for VREFEXT                                                                                                                                                                                                                                                                                                                                                                     |

Table 1. Change record

| Version | Date           | Sections         | Note                                                                                                                                                         |

|---------|----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.0     | 2017 October   | Front            | Changed status of document to data sheet after qualification.                                                                                                |

|         |                | Front            | Clarified non-support for coldspare and failsafe and updated                                                                                                 |

|         |                |                  | typical power consumption                                                                                                                                    |

|         |                | 1.4 (Table 2)    | Added missing acronyms                                                                                                                                       |

|         |                | 3 (Table 12)     | Clarified non-support for coldspare and failsafe                                                                                                             |

|         |                | 15.1 (Table 133) | Updated absolute maximum rating                                                                                                                              |

|         |                | 15.2 (Table 134) | Updated recommended operating conditions                                                                                                                     |

|         |                | 15.3 (Table 135) | Updated maximum power consumption                                                                                                                            |

|         |                | 15.4 (Table 135) | Clarified High level input voltage for system reset                                                                                                          |

|         |                | 15.7             | Clarified load conditions for AC parameters                                                                                                                  |

|         |                | 16.2 (Table 151) | Clarified non-support for coldspare and failsafe                                                                                                             |

|         |                | 16.3             | Corrected package lid dimensions                                                                                                                             |

| 3.1     | 2018 February  | 15.1 (Table 133) | Updated absolute maximum rating                                                                                                                              |

|         |                | 15.2 (Table 134) | Updated recommended operating conditions                                                                                                                     |

|         |                | 15.4             | Updated input capacitance value                                                                                                                              |

|         |                | 15.5             | Updated output capacitance value                                                                                                                             |

|         |                | 15.7.3           | Updated PLL lock time                                                                                                                                        |

|         |                | Table 20         | Minor corrections                                                                                                                                            |

|         |                | Table 18         | Register affected by external GPIO are clarified                                                                                                             |

|         |                | Table 16         | Register affected by external GPIO are clarified                                                                                                             |

| 3.2     | 2018 March     | 1.6              | Added Section for errata                                                                                                                                     |

|         |                | 1.6.1            | Added errata about missing first byte due to EEP insertion in a character overrun situation                                                                  |

| 3.3     | 2018 July      | 1.6.2            | Added errata about blocking output ports used for distributing multicast packets                                                                             |

| 3.4     | 2020 April     | Table 20         | Added missing RTR.RTRCFG.AI reset values                                                                                                                     |

|         |                | Table 33         | Clarified reset behavior of RTR.RTRCFG.AI                                                                                                                    |

|         |                | Table 47         | Corrected bit width and default value for RTR.ISRC-TIMER.RL                                                                                                  |

|         |                | Table 27         | Corrected input signal for setting reset value of the clock divi-                                                                                            |

|         |                | Table 36         | sor. Added bit description of Run-state clock divisor (RD) and Initialization clock divisor (ID)                                                             |

|         |                | 6.2.20           | Added reference reset values used in formulas                                                                                                                |

|         |                | Table 12         | Added to reference to register initialized by SPWCLKDIV                                                                                                      |

| 3.5     | 2020 June      | Table 44         | Corrected address for RTR.ISR1 register                                                                                                                      |

| 3.6     | 2020 August    | Table 27         | Corrected description for the RTR.PCTRL.PR bit. Bit is double mapped in RTR.RTACTRL.PR. Priority is explained in the description for the RTR.RTACTRL.PR bit. |

| 3.7     | 2020 November  | Table 152        | Corrected names in the package dimension table.                                                                                                              |

| 3.8     | 2021 September | Table 133        | Clarified absolute maximum current for VREFEXT pins                                                                                                          |

|         |                | Table 136        | Corrected VREFEXT pin leakage description                                                                                                                    |

|         |                | 6.5.1.1          | Defined implicit return address feature implemented.                                                                                                         |

# 1.4 Acronyms

Table 2. Acronyms

| Acronym         | Comment                                                          |  |

|-----------------|------------------------------------------------------------------|--|

| AHB             | Advanced High-performance bus, part of [AMBA]                    |  |

| AMBA            | Advanced Microcontroller Bus Architecture                        |  |

| APB             | Advanced Peripheral Bus, part of [AMBA]                          |  |

| FIFO            | First-In-First-Out, refers to buffer type                        |  |

| GPIO            | General purpose input/output                                     |  |

| I/O             | Input/Output                                                     |  |

| JTAG            | Joint Test Action Group (developer of IEEE Standard 1149.1-1990) |  |

| kB              | Kilobyte, 10 <sup>3</sup> bytes                                  |  |

| KiB             | Kibibyte, 2 <sup>10</sup> bytes, unit defined in IEEE 1541-2002  |  |

| LSb             | Least significant bit                                            |  |

| LSB             | Least significant byte                                           |  |

| Mb, Mbit        | Megabit, 10 <sup>6</sup> bits                                    |  |

| MB, Mbyte       | Megabyte, 10 <sup>6</sup> bytes                                  |  |

| MiB             | Mebibyte, 2 <sup>20</sup> bytes, unit defined in IEEE 1541-2002  |  |

| MSb             | Most significant bit                                             |  |

| MSB             | Most significant byte                                            |  |

| PnP             | Plug-and-Play                                                    |  |

| RMAP            | Remote Memory Access Protocol                                    |  |

| SEE             | Single Event Effects                                             |  |

| SEL/SEU/<br>SET | Single Event Latch up/Upset/Transient                            |  |

| SoC             | System-on-Chip                                                   |  |

| SPI             | Serial Peripheral Interface                                      |  |

| TID             | Total Ionizing Dose                                              |  |

| UART            | Universal Asynchronous Receiver/Transmitter                      |  |

## 1.5 SpaceWire routing introduction

This section provides a short introduction to SpaceWire routing, and introduces the terminology used throughout this document. For more details regarding SpaceWire, please refer to ECSS-E-ST-50-12C [SPW]. Note that GR718B provides routing features not described in this section. For more details regarding these features, please see section 6.

When a SpaceWire packet arrives on an input port of a router the first byte of the packet is used as an address to determine which port the packet should be routed to. If the first byte has a value of 0x01-0x1F it is said to be a physical address (or path address), meaning that it corresponds to an actual physical port of a router. If the first byte has a value of 0x20 - 0xFF it is said to be a logical address. If the first byte has value 0x00, the packet is always routed to the router's internal configuration port.

A packet may contain more than one address byte, but each router only looks at the first address byte when determining how to route the packet. The router may or may not, depending on how it is configured, remove the first address byte before forwarding the packet. This is called header deletion. For physical addresses, header deletion is mandatory, which means that each router that the packet passes through will use a different address byte when routing the packet. The physical addresses thus creates a path for the packet through the network. For logical addresses, header deletion is optional, allowing both logical addresses to be used across the whole network, and multiple level logical addressing.

The information on how to route packets with a specific address is stored in the routing table. The routing table in GR718B is a look-up table with 255 entries, one for each physical and logical address. Each entry in the routing table contains information about which port(s) the packet should be routed to, information whether or not header deletion should be used, as well as some other features described in more detail in section 6.2.1.

Once the route for the packet has been determined, the router's switch matrix connects the input port (the port that the packet was received on) to the output port (the port that the packet should be transmitted on). This connection is called a wormhole. When the packet transfer is finished, the wormhole is closed.

The switch matrix in GR718B can create wormholes between any ports. A port can only be an input for one wormhole at a time, and only be an output for one wormhole at a time. However, a port can be both an input and an output simultaneously, and the port's two wormholes can be connected to different ports. For example, a wormhole can be created where port 1 is an input and port 2 is an output. At the same time another wormhole can be created where port 3 is an input and port 1 is an output. Note that wormholes are not created between the actual SpaceWire link interfaces, they are created only through the switch matrix. This means that the link interfaces on the different sides of a wormhole can operate at different link speeds. The interface between the link interfaces and the switch matrix in GR718B consists of transmit and receive FIFOs with 64 entries each. The wormhole stays open either until the last byte of the packet has been read from the input port's receive FIFO and written to the output port's transmit FIFO, or until the router decides that the packet should be spilled (see section 6 for details).

### 1.6 Errata

## 1.6.1 Missing first byte after EEP on links with downstream congestion

Input port overrun protection can cause the insertion of an Error End of Packet (EEP) to overwrite the first byte of the next packet, when transfer is resumed. For more information about overrun protection see 6.2.12.

Missing first byte after EEP on link with downstream congestion occurs when all of the following conditions are met:

- Input port is configured to use overrun time-out protection. See 6.2.12 for more information.

- Flow control causes output buffer to be entirely filled.

- Overrun time-out has occurred in the input buffer, the current packet is discarded in the input buffer, EEP is scheduled for insertion in the output buffer.

- Output port is resuming normal operation after receiving flow control token, i.e. the downstream receiver is able to accept data.

- After the output port resumes normal operation, the following packet is routed from the same input port as the packet that was discarded and terminated with EEP.

Workaround 1: Disable overrun protection, and if possible move the overrun protection to the end node.

### 1.6.2 Blocking output ports used for distributing multicast packets

When a subset of the output ports are busy sending a packet, an incoming multicast packet will allocate the available outputs ports and then wait for all output ports to become available. If another multicast packet with higher priority (lower input port number) that will be routed to the same set of ports is sent to the router, this packet will allocate the currently occupied output ports when they become available. This results in a blocking state where multiple multicast packets, each allocating a subset of the output ports, blocks each other.

Triggering a blocking state occurs when all of the following conditions are met:

- Sending multicast packets distributed to multiple output ports from multiple input ports while also sending packets to only a subset of the same output ports.

- Multicast packet with higher priority (lower input port number) is received at the router when multicast packet with lower priority only has successfully allocated a subset of the output ports.

Workaround 1: All packets routed to output ports within a packet distribution group should use the same routing configuration and packet distribution mapping.

## 2 Architecture

### 2.1 Overview

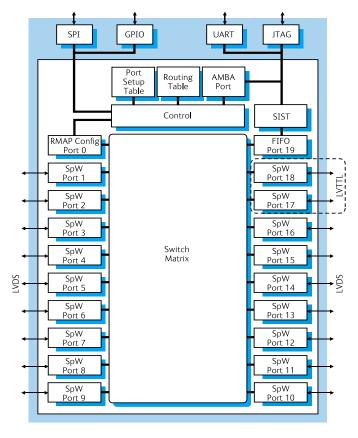

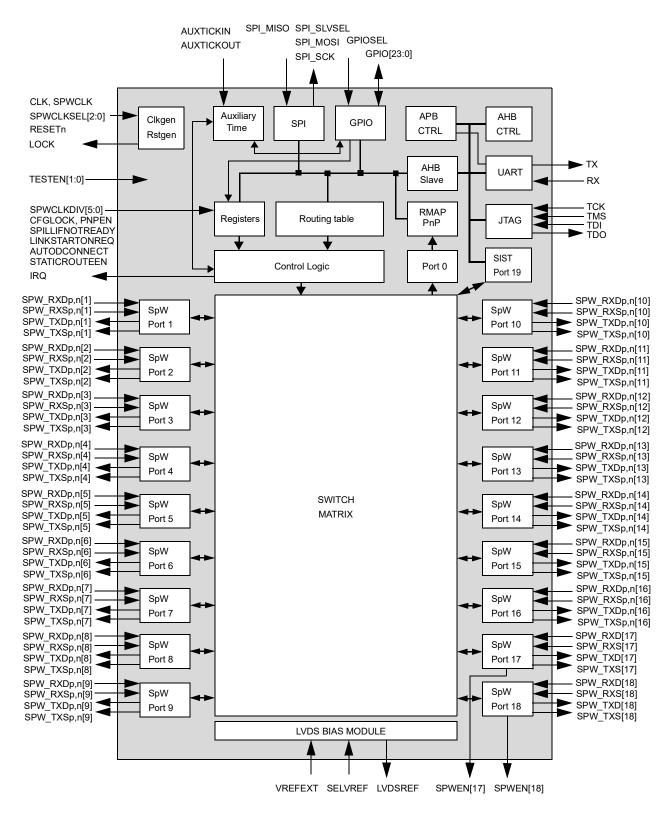

The GR718B - Radiation Tolerant 18x SpaceWire Router architecture is centered around a non-blocking switch matrix which can connect any input port to any output port.

All the addressing modes, such as path, logical, and regional logical addressing are supported. Group adaptive routing is fully supported, meaning that both path and logical addresses can be individually configured to use one or more output ports. A unique feature is the support for packet distribution, which can be used to implement multicast and broadcast addressing. Output ports are arbitrated using two priority levels with a round-robin scheme within each level.

The 18x SpaceWire router implements 18 external SpaceWire ports, an internal configuration port, that gives access to configuration and status registers, and also an internal port for system level testing. Out of the external SpaceWire ports, 16 have on-chip non-cold-spare LVDS transceivers, and two have LVTTL interfaces to off-chip LVDS transceivers. For noisy environment or protection from various failures such as open inputs, floating inputs or shorted inputs an external fail-safe function should be considered for all active SpaceWire LVDS inputs.

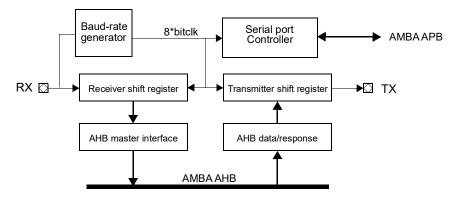

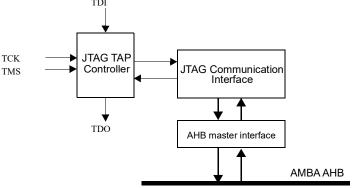

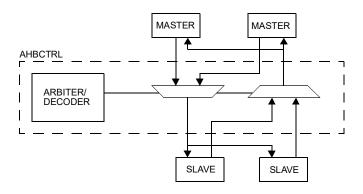

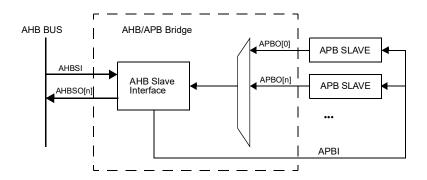

There is also an on-chip AMBA Advanced High-speed Bus (AHB) which hosts UART and JTAG interfaces that are AHB masters. The router's configuration port contains an AHB slave interface which is connected to the AHB bus, and allows the configuration port registers to be accessed from the UART and JTAG interfaces.

An auxiliary time-code / distributed interrupt code interface is present, for sending and receiving time-codes / distributed interrupt codes through external pins. Parts of the interface use dedicated pins, while the rest are multiplexed on the GPIO[23:0] pins.

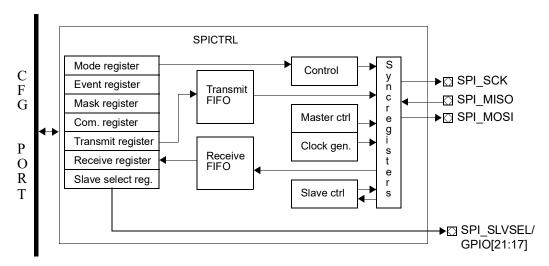

There are SPI and GPIO interfaces accessible through the configuration port, which allows SPI devices to be accessed, and general purpose signalling to be performed, directly through RMAP commands, or through the UART and JTAG interfaces.

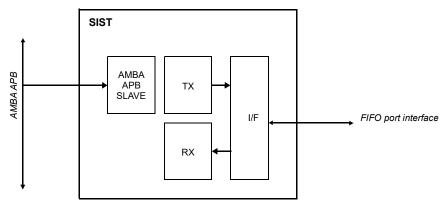

The full SpaceWire router architecture includes the following modules: SpaceWire Router, SPI Controller, UART Interface, JTAG Interface, General Purpose I/O Interface, SpaceWire In-System Test (SIST), System Level Test Configuration, AMBA AHB controller and AMBA APB controller.

Figure 1. Block diagram and signal overview

## 2.2 Cores

GR718B is based on cores from the GRLIB IP library. The cores used are listed in table 3. The vendor and device identifiers shown in the last two columns can be extracted from the AMBA plug & play information.

Table 3. Used IP cores

| Core        | Function                        | Vendor | Device |

|-------------|---------------------------------|--------|--------|

| AHBCTRL     | AHB Arbiter & Decoder           | 0x01   | -      |

| APBCTRL     | AHB/APB Bridge                  | 0x01   | 0x006  |

| GRSPWROUTER | SpaceWire Router                | 0x01   | 0x08B  |

| GRGPIO      | General Purpose I/O Interface   | 0x01   | 0x01A  |

| AHBUART     | UART Interface                  | 0x01   | 0x007  |

| AHBJTAG     | JTAG Interface                  | 0x01   | 0x01C  |

| SPICTRL     | SPI Controller                  | 0x01   | 0x02D  |

| GRSPW2_SIST | SpaceWire In-System Test        | 0x01   | 0x091  |

| GRGPREG     | System Level Test Configuration | 0x01   | 0x087  |

## 2.3 Memory map

GR718B provides three different address spaces: AMBA address space, RMAP address space, and SpaceWire Plug-and-Play address space. The AMBA address space is accessible through the JTAG and UART interfaces. The RMAP address space is accessible through RMAP commands to the router's configuration port. The SpaceWire Plug-and-Play address space is accessible through Space-Wire Plug-and-Play commands to the router's configuration port. Table 4, 5, and 6 shows an overview of the three different address spaces, while section 2.4 contains a complete list of all the GR718B registers, showing the addresses for all three address spaces. The AMBA plug & play information is detailed in section 2.3.1.

Table 4. AMBA AHB address space

| Core        | Address range           | Comment                                   |

|-------------|-------------------------|-------------------------------------------|

| APBCTRL     | 0xFFE00000 - 0xFFEFFFFC | AMBA APB bridge                           |

| AHBUART     | 0xFFE00000 - 0xFFE000FC | UART interface registers                  |

| GRGPREG     | 0xFFE00100 - 0xFFE001FC | System Level Test Configuration registers |

| GRSPW2_SIST | 0xFFE00200 - 0xFFE002FC | SpaceWire In-System Test registers        |

| APBCTRL     | 0xffEff000 - 0xffE0ffff | AMBA APB plug & play area                 |

| GRSPWROUTER | 0xFFF20000 - 0xFFF21FFC | SpaceWire Router registers                |

| SPICTRL     | 0xFFF22000 - 0xFFF220FC | SPI controller registers                  |

| GRPGIO      | 0xFFF22100 - 0xFFF221FC | General purpose I/O interface registers   |

| AHBCTRL     | 0xFFFFF000 - 0xFFFFFFF  | AMBA AHB plug & play area                 |

Note: An access to an undefined address will cause an AHB error response. A read access to a reserved address within a defined range will return zero, while a write access will have no effect.

Table 5. RMAP address space

| Core        | Address range           | Comment                                                |

|-------------|-------------------------|--------------------------------------------------------|

| GRSPWROUTER | 0x00000000 - 0x00001FFC | SpaceWire Router registers                             |

| SPICTRL     | 0x00002000 - 0x000020FC | SPI controller registers                               |

| GRPGIO      | 0x00002100 - 0x000021FC | General purpose I/O interface registers                |

| N/A         | 0x00002200 - 0x00002FFC | Reserved range. Read return zero. Write has no effect. |

Note: An RMAP access to an undefined address will result in an error. See section 6.5.1 for details.

Table 6. SpaceWire Plug-and-Play address space

| Core        | Address range           | Comment                           |

|-------------|-------------------------|-----------------------------------|

| GRSPWROUTER | 0x00000000 - 0x0000C000 | SpaceWire Plug-and-Play registers |

Note: See section 6.5.4 for details about accesses to undefined addresses.

## 2.3.1 AMBA plug & play information

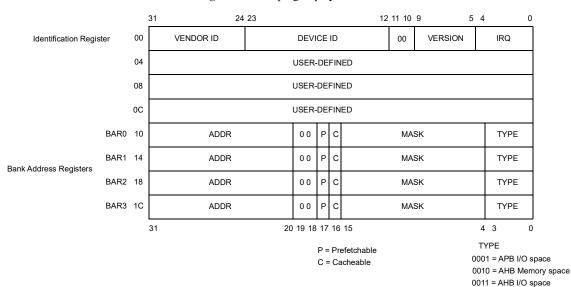

Plug & play is used on the AMBA bus to identify all cores and their configurations. The AMBA plug & play memory map is shown in table 7, and the two different plug & play record types are detailed in figure 2 and 3. Both the AHB and APB plug & play information are mapped at read-only address areas. Note that AMBA plug & play is not available for the SPI controller or General purpose I/O interface, mapped in the SpaceWire router configuration port area.

Also note that AMBA plug & play is not to be confused with the SpaceWire-Plug-and-Play, which is used for identifying the SpaceWire characteristics through the configuration port of the router. Space-Wire Plug-and-Play is described in section 6.5.4.

Table 7. AMBA plug & play memory map

| Core        | Function                        | Туре       | Index | Address range           |

|-------------|---------------------------------|------------|-------|-------------------------|

| AHBJTAG     | JTAG interface                  | AHB master | 0     | 0xFFFFF000 - 0xFFFFF01F |

| AHBUART     | UART interface                  | AHB master | 1     | 0xFFFFF020 - 0xFFFFF03F |

|             |                                 | APB slave  | 0     | 0xFFEFF000 - 0xFFEFF007 |

| APBCTRL     | AHB/APB Bridge                  | AHB slave  | 0     | 0xFFFFF800 - 0xFFFFF81F |

| GRSPWROUTER | SpaceWire Router                | AHB slave  | 1     | 0xFFFFF820 - 0xFFFFF83F |

| GRGPREG     | System Level Test Configuration | APB slave  | 1     | 0xFFEFF008 - 0xFFEFF00F |

| GRSPW2_SIST | SpaceWire In-System Test        | APB slave  | 2     | 0xFFEFF010 - 0xFFEFF017 |

Figure 2. AHB plug & play information record

Figure 3. APB plug & play information record

24 23 31 12 11 10 9 5 APB Plug&play record Configuration word VENDOR ID DEVICE ID 00 VERSION IRQ ADDR MASK TYPE BAR 0x04 31 20 19

# 2.4 Register overview

Table 8 contains an overview of all GR718B registers and shows which AMBA address, RMAP address, and SpaceWire Plug-and-Play address they are mapped to. Detailed descriptions of the registers are found in the section where the corresponding function is described. Note that unlisted addresses are reserved.

Table 8. GR718B register overview

| Register name                                              | Register acronym          | AMBA address               | RMAP address               | SpW PnP address |

|------------------------------------------------------------|---------------------------|----------------------------|----------------------------|-----------------|

| SpaceWire                                                  | Router registers (section | on 6.5.3)                  |                            |                 |

| Routing table port mapping, physical addresses 1-19        | RTR.RTPMAP                | 0xFFF20004 -<br>0xFFF2004C | 0x00000004 -<br>0x0000004C |                 |

| Routing table port mapping, logical addresses 32-255       | RTR.RTPMAP                | 0xFFF20080 -<br>0xFFF203FC | 0x00000080 -<br>0x000003FC |                 |

| Routing table address control, physical addresses 1-19     | RTR.RTACTRL               | 0xFFF20404 -<br>0xFFF2044C | 0x00000404 -<br>0x0000044C |                 |

| Routing table address control, logical addresses 32-255    | RTR.RTACTRL               | 0xFFF20480 -<br>0xFFF207FC | 0x00000480 -<br>0x000007FC |                 |

| Port control, port 0 (configuration port)                  | RTR.PCTRLCFG              | 0xFFF20800                 | 0x00000800                 |                 |

| Port control, ports 1-19 (SpaceWire ports and SIST port)   | RTR.PCTRL                 | 0xFFF20804 -<br>0xFFF2084C | 0x00000804 -<br>0x0000084C |                 |

| Port status, port 0 (configuration port)                   | RTR.PSTSCFG               | 0xFFF20880                 | 0x00000880                 |                 |

| Port status, ports 1-19 (SpaceWire ports and SIST port)    | RTR.PSTS                  | 0xFFF20884 -<br>0xFFF208CC | 0x00000884 -<br>0x000008CC |                 |

| Port timer reload, ports 0-19                              | RTR.PTIMER                | 0xFFF20900 -<br>0xFFF2094C | 0x00000900 -<br>0x0000094C |                 |

| Port control 2, port 0 (configuration port)                | RTR.PCTRL2CFG             | 0xFFF20980                 | 0x00000980                 |                 |

| Port control 2, ports 1-19 (SpaceWire ports and SIST port) | RTR.PCTRL2                | 0xFFF20984 -<br>0xFFF209CC | 0x00000984 -<br>0x000009CC |                 |

| Router configuration / status                              | RTR.RTRCFG                | 0xFFF20A00                 | 0x00000A00                 |                 |

| Time-code                                                  | RTR.TC                    | 0xFFF20A04                 | 0x00000A04                 |                 |

| Version / instance ID                                      | RTR.VER                   | 0xFFF20A08                 | 0x00000A08                 |                 |

| Initialization divisor                                     | RTR.IDIV                  | 0xFFF20A0C                 | 0x00000A0C                 |                 |

| Configuration write enable                                 | RTR.CFGWE                 | 0xFFF20A10                 | 0x00000A10                 |                 |

| Timer prescaler reload                                     | RTR.PRESCALER             | 0xFFF20A14                 | 0x00000A14                 |                 |

| Interrupt mask                                             | RTR.IMASK                 | 0xFFF20A18                 | 0x00000A18                 |                 |

| Interrupt port mask                                        | RTR.IPMASK                | 0xFFF20A1C                 | 0x00000A1C                 |                 |

| Port interrupt pending                                     | RTR.PIP                   | 0xFFF20A20                 | 0x00000A20                 |                 |

| Interrupt code generation                                  | RTR.ICODEGEN              | 0xFFF20A24                 | 0x00000A24                 |                 |

| Interrupt code distribution ISR, interrupt 0-31            | RTR.ISR0                  | 0xFFF20A28                 | 0x00000A28                 |                 |

| Interrupt code distribution ISR, interrupt 32-63           | RTR.ISR1                  | 0xFFF20A2C                 | 0x00000A2C                 |                 |

| Interrupt code distribution ISR timer reload               | RTR.ISRTIMER              | 0xFFF20A30                 | 0x00000A30                 |                 |

| Interrupt code distribution ACK-to-INT timer reload        | RTR.AITIMER               | 0xFFF20A34                 | 0x00000A34                 |                 |

| Interrupt code distribution ISR change timer reload        | RTR.ISRCTIMER             | 0xFFF20A38                 | 0x00000A38                 |                 |

| SpaceWire link running status                              | RTR.LRUNSTS               | 0xFFF20A40                 | 0x00000A40                 |                 |

Table 8. GR718B register overview

| Register name                                                              | Register acronym | AMBA address                            | RMAP address                            | SpW PnP<br>address |

|----------------------------------------------------------------------------|------------------|-----------------------------------------|-----------------------------------------|--------------------|

| Capability                                                                 | RTR.CAP          | 0xFFF20A44                              | 0x00000A44                              |                    |

| SpaceWire Plug-and-Play - Device Vendor and Product ID                     | RTR.PNPVEND      | 0xFFF20A50                              | 0x00000A50                              | 0x00000000         |

| SpaceWire Plug-and-Play - Unit Vendor and Product ID                       | RTR.PNPUVEND     | 0xFFF20A54                              | 0x00000A54                              | 0x00000009         |

| SpaceWire Plug-and-Play - Unit Serial<br>Number                            | RTR.PNPUSN       | 0xFFF20A58                              | 0x00000A58                              | 0x0000000A         |

| Outgoing character counter, ports 1-19                                     | RTR.OCHARCNT     | 0xFFF20C10,<br>0xFFF20C20<br>0xFFF20D30 | 0x00000C10,<br>0x00000C20<br>0x00000D30 |                    |

| Incoming character counter, ports 1-19                                     | RTR.ICHARCNT     | 0xFFF20C14,<br>0xFFF20C24<br>0xFFF20D34 | 0x00000C14,<br>0x00000C24<br>0x00000D34 |                    |

| Outgoing packet counter, ports 1-19                                        | RTR.OPKTCNT      | 0xFFF20C18,<br>0xFFF20C28<br>0xFFF20D38 | 0x00000C18,<br>0x00000C28<br>0x00000D38 |                    |

| Incoming packet counter, ports 1-19                                        | RTR.IPKTCNT      | 0xFFF20C1C,<br>0xFFF20C2C<br>0xFFF20D3C | 0x00000C1C,<br>0x00000C2C<br>0x00000D3C |                    |

| Maximum packet length, ports 0-19                                          | RTR.MAXPLEN      | 0xFFF20E00 -<br>0xFFF20E4C              | 0x00000E00 -<br>0x00000E4C              |                    |

| Credit counter, ports 1-18                                                 | RTR.CREDCNT      | 0xFFF20E84 -<br>0xFFF20EC8              | 0x00000E84 -<br>0x00000EC8              |                    |

| General purpose out, bits 0-31                                             | RTR.GPOA         | 0xFFF20F00                              | 0x00000F00                              |                    |

| General purpose out, bits 32-48                                            | RTR.GPOB         | 0xFFF20F04                              | 0x00000F04                              |                    |

| General purpose in, bits 0-1                                               | RTR.GPIA         | 0xFFF20F10                              | 0x00000F10                              |                    |

| Routing table, combined port mapping and address control, addresses 1-19   | RTR.RTCOMB       | 0xFFF21004 -<br>0xFFF2104C              | 0x00001004 -<br>0x0000104C              |                    |

| Routing table, combined port mapping and address control, addresses 32-255 | RTR.RTCOMB       | 0xFFF21080 -<br>0xFFF213FC              | 0x00001080 -<br>0x000013FC              |                    |

| SpaceWire Plug-and-Play - Version                                          | RTR.PNPVER       |                                         |                                         | 0x00000001         |

| SpaceWire Plug-and-Play - Device Status                                    | RTR.PNPDEVSTS    |                                         |                                         | 0x00000002         |

| SpaceWire Plug-and-Play - Active Links                                     | RTR.PNPACTLNK    |                                         |                                         | 0x00000003         |

| SpaceWire Plug-and-Play - Link Information                                 | RTR.PNPLNKINFO   |                                         |                                         | 0x00000004         |

| SpaceWire Plug-and-Play - Owner<br>Address 0                               | RTR.PNPOA0       |                                         |                                         | 0x00000005         |

| SpaceWire Plug-and-Play - Owner<br>Address 1                               | RTR.PNPOA1       |                                         |                                         | 0x00000006         |

| SpaceWire Plug-and-Play - Owner<br>Address 2                               | RTR.PNPOA2       |                                         |                                         | 0x00000007         |

| SpaceWire Plug-and-Play - Device ID                                        | RTR.PNPDEVID     |                                         |                                         | 0x00000008         |

| SpaceWire Plug-and-Play - Vendor String<br>Length                          | RTR.PNPVSTRL     |                                         |                                         | 0x00004000         |

| SpaceWire Plug-and-Play - Product<br>String Length                         | RTR.PNPPSTRL     |                                         |                                         | 0x00006000         |

| SpaceWire Plug-and-Play - Protocol<br>Count                                | RTR.PNPPCNT      |                                         |                                         | 0x00008000         |

| SpaceWire Plug-and-Play - Application<br>Count                             | RTR.PNPACNT      |                                         |                                         | 0x0000C000         |

Table 8. GR718B register overview

| Register name                       | Register acronym             | AMBA address               | RMAP address | SpW PnP<br>address |

|-------------------------------------|------------------------------|----------------------------|--------------|--------------------|

| SpaceWire l                         | In-System Test registers (se | ection 7.3)                |              |                    |

| SpaceWire Address Register 0-7      | SIST.ADDR[0-7]               | 0xFFE00200 -<br>0xFFE0021C |              |                    |

| Protocol ID and Polynomial Register | SIST.PID                     | 0xFFE00220                 |              |                    |

| Seed Register                       | SIST.SEED                    | 0xFFE00224                 |              |                    |

| Packet Length Register              | SIST.LEN                     | 0xFFE00228                 |              |                    |

| Control Register                    | SIST.CTRL                    | 0xFFE0022C                 |              |                    |

| Error Register 0                    | SIST.ERROR0                  | 0xFFE00230                 |              |                    |

| Error Register 1                    | SIST.ERROR1                  | 0xFFE00234                 |              |                    |

| Error Register 2                    | SIST.ERROR2                  | 0xFFE00238                 |              |                    |

| Packet Counter Register             | SIST.PKTCNTR                 | 0xFFE0023C                 |              |                    |

| Timer Register 0                    | SIST.TIMER0                  | 0xFFE00240                 |              |                    |

| Timer Register 1                    | SIST.TIMER1                  | 0xFFE00244                 |              |                    |

| Status Register                     | SIST.STAT                    | 0xFFE00248                 |              |                    |

| State Register                      | SIST.STATE                   | 0xFFE0024C                 |              |                    |

| Transmitter Byte Count Register     | SIST.TXBYTECNTR              | 0xFFE00250                 |              |                    |

| Receiver Byte Count Register        | SIST.RXBYTECNTR              | 0xFFE00254                 |              |                    |

| Time-Code Register                  | SIST.TIME                    | 0xFFE00258                 |              |                    |

| Protection Register                 | SIST.PROT                    | 0xFFE0025C                 |              |                    |

| Data Input Registers 0 - 7          | SIST.DIN[0-7]                | 0xFFE00280 -<br>0xFFE0029C |              |                    |

| Data Output Registers 0 - 7         | SIST.DOUT[0-7]               | 0xFFE002A0 -<br>0xFFE002BC |              |                    |

| UART                                | Interface registers (section | 1 8.3)                     | •            |                    |

| AHB UART status register            | UART.STS                     | 0xFFE00004                 |              |                    |

| AHB UART control register           | UART.CTRL                    | 0xFFE00008                 |              |                    |

| AHB UART scaler register            | UART.SCALE                   | 0xFFE0000C                 |              |                    |

| SPI Co                              | ntroller registers (section  | 10.3)                      |              |                    |

| Capability register                 | SPI.CAP                      | 0xFFF22000                 | 0x00002000   |                    |

| Mode register                       | SPI.MODE                     | 0xFFF22020                 | 0x00002020   |                    |

| Event register                      | SPI.EVENT                    | 0xFFF22024                 | 0x00002024   |                    |

| Mask register                       | SPI.MASK                     | 0xFFF22028                 | 0x00002028   |                    |

| Command register                    | SPI.CMD                      | 0xFFF2202C                 | 0x0000202C   |                    |

| Transmit register                   | SPI.TX                       | 0xFFF22030                 | 0x00002030   |                    |

| Receive register                    | SPI.RX                       | 0xFFF22034                 | 0x00002034   |                    |

Table 8. GR718B register overview

| Register name                     | Register acronym          | AMBA address   | RMAP address | SpW PnP<br>address |

|-----------------------------------|---------------------------|----------------|--------------|--------------------|

| Slave Select register (optional)  | SPI.SLVSEL                | 0xFFF22038     | 0x00002038   |                    |

| Automatic slave select register   | SPI.ASLVSEL               | 0xFFF2203C     | 0x0000203C   |                    |

| General Purpose                   | I/O Interface registers ( | section 11.2)  |              |                    |

| I/O port data register            | GPIO.DATA                 | 0xFFF22100     | 0x00002100   |                    |

| I/O port output register          | GPIO.OUT                  | 0xFFF22104     | 0x00002104   |                    |

| I/O port direction register       | GPIO.DIR                  | 0xFFF22108     | 0x00002108   |                    |

| Capability register               | GPIO.CAP                  | 0xFFF2211C     | 0x0000211C   |                    |

| System Level Test                 | Configuration registers   | (section 12.1) |              |                    |

| System level test configuration 1 | SYSTEST.CFG1              | 0xFFE00100     |              |                    |

| System level test configuration 2 | SYSTEST.CFG2              | 0xFFE00104     |              |                    |

An example register, showing the register layout used throughout this document, can be seen in table 9. The values used for the reset value fields are described in table 10, and the values used for the field type fields are described in table 11. Fields that are named RESERVED, RES, or R are read-only fields that always reads as zero.

Table 9. <Address> - <Register acronym> - <Register name>