## FRONTGRADE

# **Dual-Core LEON3FT SPARC V8 Processor**

# GR712RC

# **Dual-Core LEON3FT SPARC V8 Processor**

# User's Manual

### **Table of contents**

| 1 | Intro | Introduction                                         |    |  |  |

|---|-------|------------------------------------------------------|----|--|--|

|   | 1.1   | Scope                                                | 7  |  |  |

|   | 1.2   | GR712RC Architecture                                 | 7  |  |  |

|   | 1.3   | Memory map                                           | 8  |  |  |

|   | 1.4   | Interrupts                                           | 9  |  |  |

|   | 1.5   | GRLIB IP cores                                       | 10 |  |  |

|   | 1.6   | References                                           | 11 |  |  |

|   | 1.7   | Errata                                               | 12 |  |  |

|   | 1.8   | Document revision history                            | 20 |  |  |

| 2 | Signa | als and I/O Switch Matrix                            | 27 |  |  |

|   | 2.1   | Switch matrix functions listed per pin               | 28 |  |  |

|   | 2.2   | Switch matrix pins listed by function                | 32 |  |  |

|   | 2.3   | Function conflicts, enable conditions and fixed pins | 35 |  |  |

| 3 | Cloc  | king                                                 | 37 |  |  |

|   | 3.1   | System clock                                         |    |  |  |

|   | 3.2   | SpaceWire clock                                      |    |  |  |

|   | 3.3   | MIL-STD-1553                                         |    |  |  |

|   | 3.4   | Telemetry                                            |    |  |  |

|   | 3.5   | Telecommand                                          |    |  |  |

|   | 3.6   | Obsolete                                             |    |  |  |

|   | 3.7   | SLINK                                                | 38 |  |  |

|   | 3.8   | SDRAM clock                                          | 39 |  |  |

|   | 3.9   | Clock gating unit                                    | 39 |  |  |

|   | 3.10  | Test mode clocking                                   | 40 |  |  |

| 4 | LEO   | N3FT - High-performance SPARC V8 32-bit Processor    | 41 |  |  |

|   | 4.1   | Overview                                             |    |  |  |

|   | 4.2   | LEON3 integer unit.                                  |    |  |  |

|   | 4.3   | Instruction cache                                    |    |  |  |

|   | 4.4   | Data cache                                           |    |  |  |

|   | 4.5   | Additional cache functionality                       |    |  |  |

|   | 4.6   | Memory management unit                               | 53 |  |  |

|   | 4.7   | Floating-point unit                                  |    |  |  |

|   | 4.8   | Error detection and correction                       |    |  |  |

|   | 4.9   | Signal definitions                                   | 57 |  |  |

| 5 | Fault | t Tolerant Memory Controller                         | 58 |  |  |

|   | 5.1   | Overview                                             |    |  |  |

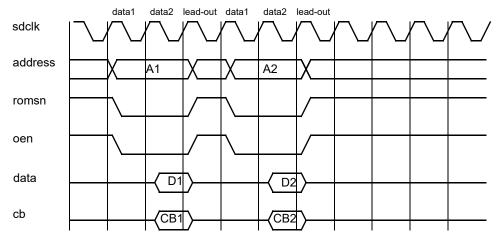

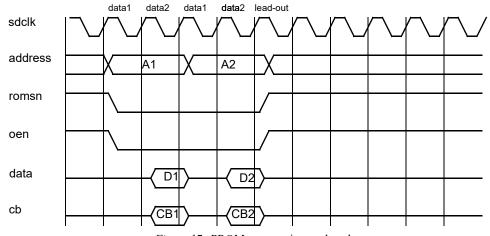

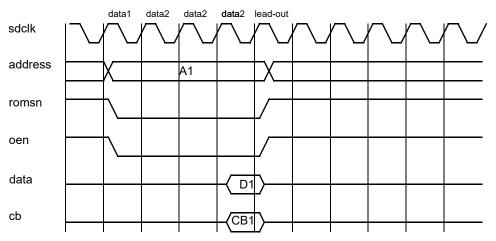

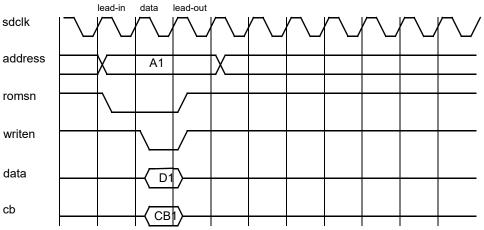

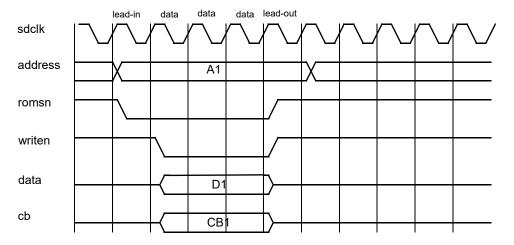

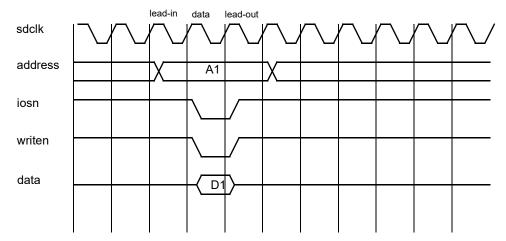

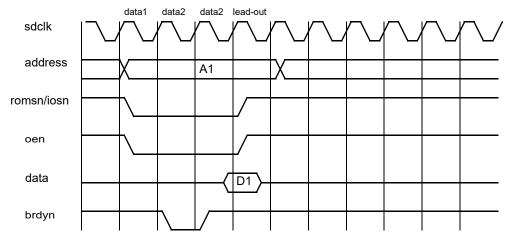

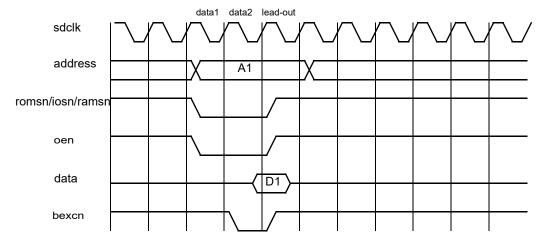

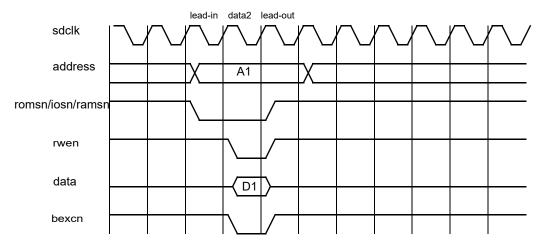

|   | 5.2   | PROM access                                          | 59 |  |  |

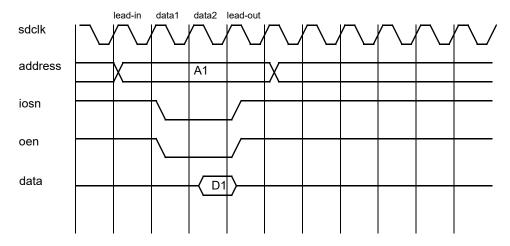

|   | 5.3   | Memory mapped IO                                     | 61 |  |  |

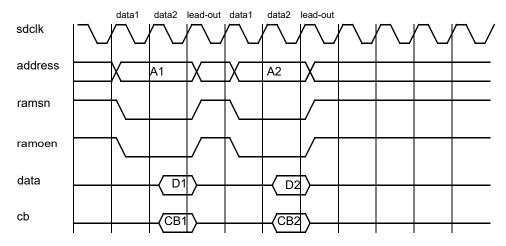

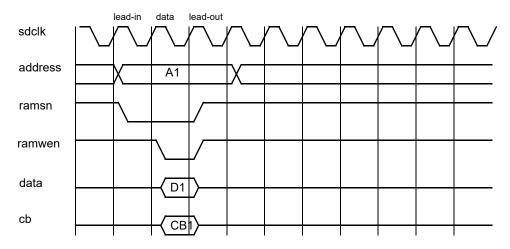

|   | 5.4   | SRAM access                                          | 62 |  |  |

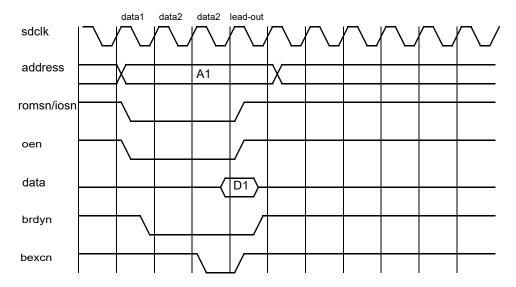

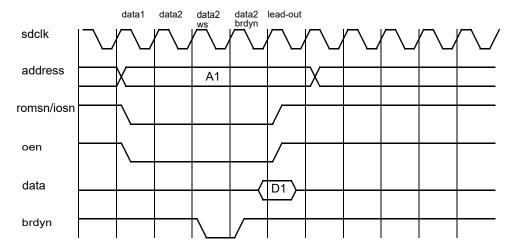

|   | 5.5   | 8-bit PROM and SRAM access                           | 63 |  |  |

|   | 5.6   | 8- bit I/O access                                    | 64 |  |  |

|   | 5.7   | Burst cycles                                         | 64 |  |  |

|   | 5.8   | SDRAM access                                         | 64 |  |  |

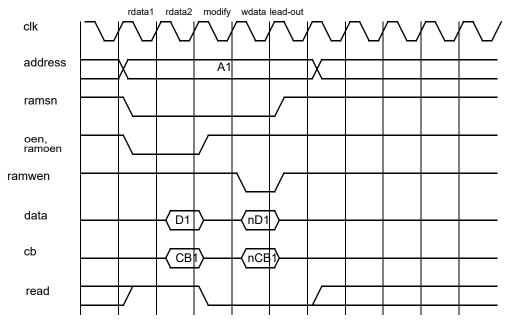

|    | 5.9  | Memory EDAC                                       | 66  |

|----|------|---------------------------------------------------|-----|

|    | 5.10 | Bus Ready signalling                              | 69  |

|    | 5.11 | External bus errors                               | 70  |

|    | 5.12 | Read strobe                                       | 71  |

|    | 5.13 | Registers                                         | 71  |

|    | 5.14 | Signal definitions                                | 74  |

| 6  | On-c | hip Memory with EDAC Protection                   | 75  |

|    | 6.1  | Overview                                          | 75  |

|    | 6.2  | Operation                                         | 75  |

|    | 6.3  | Registers                                         | 76  |

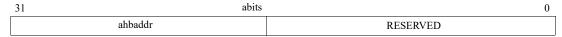

| 7  | AHB  | Status Registers                                  | 77  |

|    | 7.1  | Overview                                          | 77  |

|    | 7.2  | Operation                                         |     |

|    | 7.3  | Registers                                         | 77  |

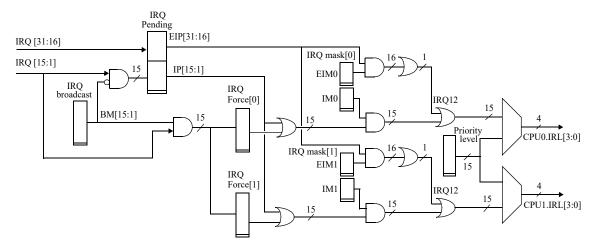

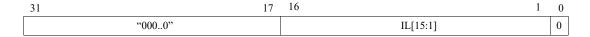

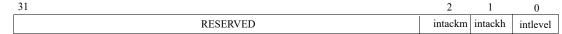

| 8  | Mult | iprocessor Interrupt Controller                   | 78  |

|    | 8.1  | Overview                                          | 78  |

|    | 8.2  | Operation                                         | 78  |

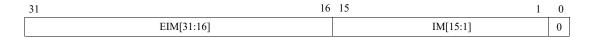

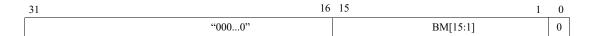

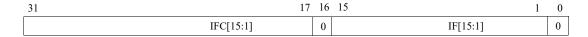

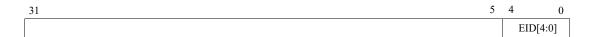

|    | 8.3  | Registers                                         | 80  |

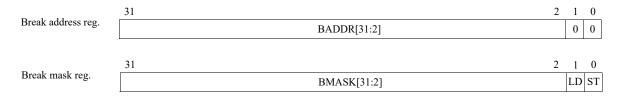

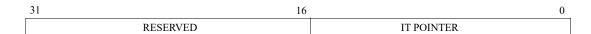

| 9  | Hard | lware Debug Support Unit                          | 83  |

|    | 9.1  | Overview                                          | 83  |

|    | 9.2  | Operation                                         | 83  |

|    | 9.3  | AHB Trace Buffer                                  | 84  |

|    | 9.4  | Instruction trace buffer                          | 85  |

|    | 9.5  | DSU memory map                                    |     |

|    | 9.6  | DSU registers                                     | 87  |

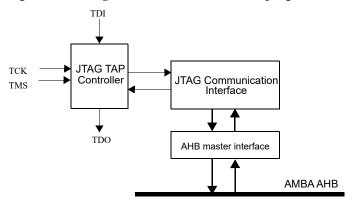

| 10 | JTA( | G Debug Interface                                 | 91  |

|    | 10.1 | Overview                                          | 91  |

|    | 10.2 | Operation                                         | 91  |

|    | 10.3 | Registers                                         | 92  |

|    | 10.4 | Signal definitions                                | 92  |

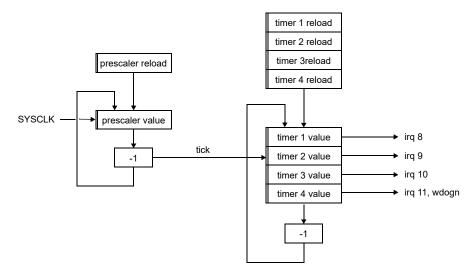

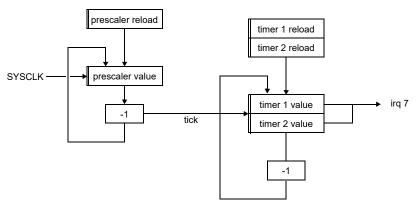

| 11 | Gene | eral Purpose Timer Unit                           | 93  |

|    | 11.1 | Overview                                          | 93  |

|    | 11.2 | Operation                                         | 93  |

|    | 11.3 | Registers                                         | 94  |

|    | 11.4 | Signal definitions                                | 95  |

| 12 | Gene | ral Purpose Timer Unit with Time Latch Capability | 96  |

|    | 12.1 | Overview                                          | 96  |

|    | 12.2 | Operation                                         | 96  |

|    | 12.3 | Registers                                         | 97  |

| 13 | Gene | ral Purpose Register                              | 99  |

|    | 13.1 | Operation                                         |     |

|    | 13.2 | Registers                                         | 99  |

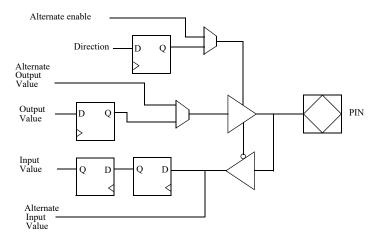

| 14 | Gene | ral Purpose I/O Port                              | 100 |

|    | 14.1 | Overview                                          | 100 |

|    | 14.2  | Operation                                   | 100 |

|----|-------|---------------------------------------------|-----|

|    | 14.3  | Registers                                   | 102 |

|    | 14.4  | Signal definitions                          | 103 |

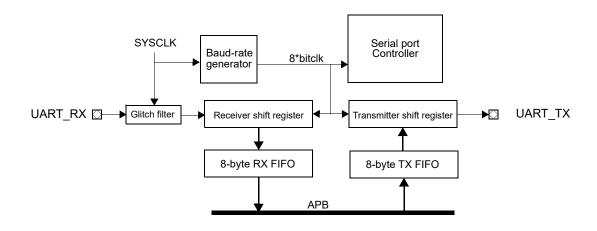

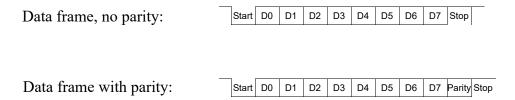

| 15 | UAR   | Γ Serial Interface                          | 104 |

|    | 15.1  | Overview                                    | 104 |

|    | 15.2  | Operation                                   | 104 |

|    | 15.3  | Baud-rate generation                        | 105 |

|    | 15.4  | Loop back mode                              | 106 |

|    | 15.5  | FIFO debug mode                             | 106 |

|    | 15.6  | Interrupt generation                        | 106 |

|    | 15.7  | Registers                                   | 106 |

|    | 15.8  | Signal definitions                          | 108 |

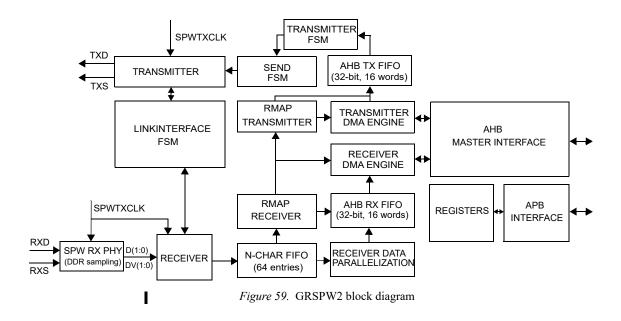

| 16 | Space | eWire Interface with RMAP support           | 109 |

|    | 16.1  | Overview                                    | 109 |

|    | 16.2  | Operation                                   | 109 |

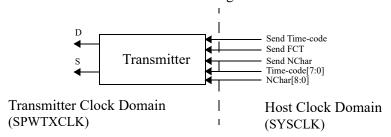

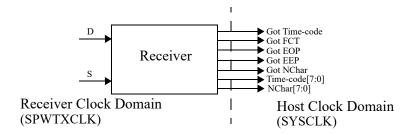

|    | 16.3  | Link interface                              | 110 |

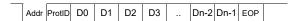

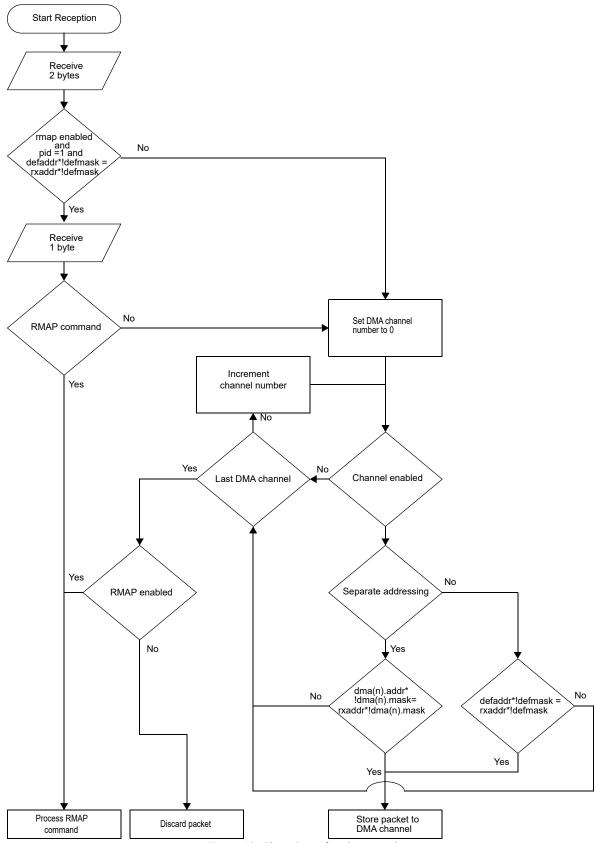

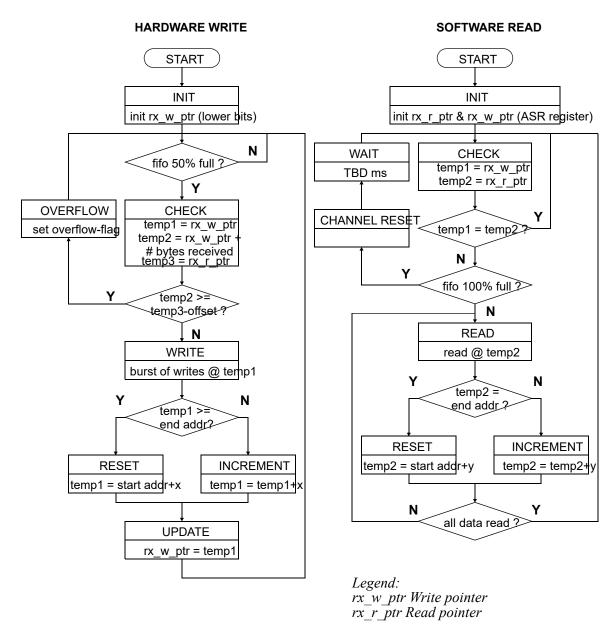

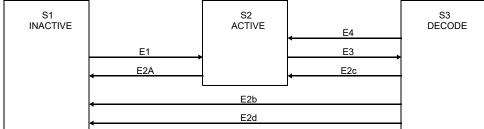

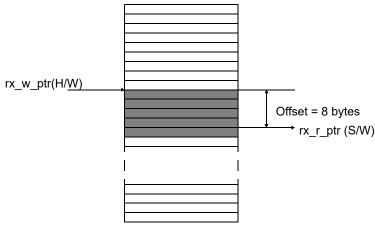

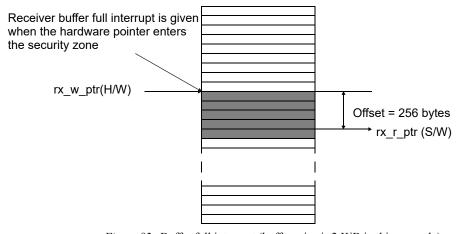

|    | 16.4  | Receiver DMA channels                       | 112 |

|    | 16.5  | Transmitter DMA channels                    | 118 |

|    | 16.6  | RMAP                                        | 121 |

|    | 16.7  | AMBA interface                              | 125 |

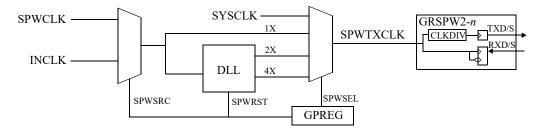

|    | 16.8  | SpaceWire clock generation                  | 126 |

|    | 16.9  | Registers                                   | 128 |

|    | 16.10 | Signal definitions                          | 133 |

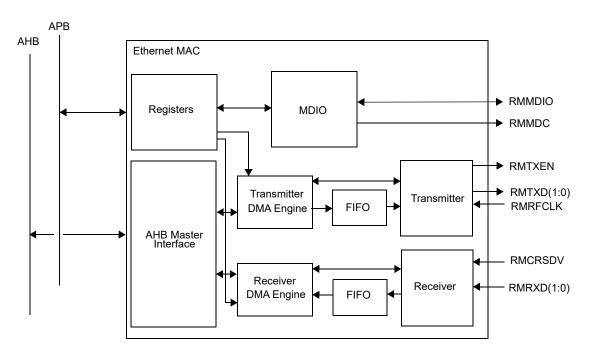

| 17 | Ether | net Media Access Controller (MAC)           | 134 |

|    | 17.1  | Overview                                    | 134 |

|    | 17.2  | Operation                                   | 134 |

|    | 17.3  | Tx DMA interface                            | 135 |

|    | 17.4  | Rx DMA interface                            | 136 |

|    | 17.5  | MDIO Interface                              | 138 |

|    | 17.6  | Reduced Media Independent Interfaces (RMII) | 138 |

|    | 17.7  | Registers                                   | 139 |

|    | 17.8  | Signal definitions                          | 142 |

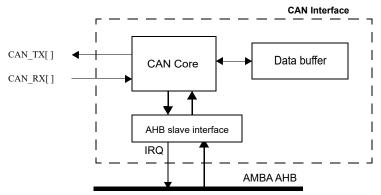

| 18 | CAN   | Interface                                   | 143 |

|    | 18.1  | Overview                                    | 143 |

|    | 18.2  | CAN controller overview                     | 143 |

|    | 18.3  | AHB interface                               | 143 |

|    | 18.4  | BasicCAN mode                               | 144 |

|    | 18.5  | PeliCAN mode                                | 148 |

|    | 18.6  | Common registers                            | 158 |

|    | 18.7  | Design considerations                       | 159 |

|    | 18.8  | Signal definitions                          | 159 |

| 19 | Obsol | lete                                        | 160 |

|    | 19.1  | Signal definitions                          | 160 |

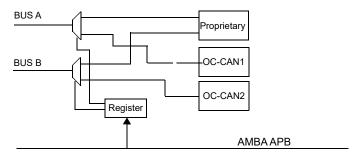

| 20 | CAN   | Bus multiplexer                             | 161 |

|    | 20.1  | Overview                                    | 161 |

|    | 20.1  | 0 101 110                                   |     |

|    | 20.2            | Operation                                    | 161 |  |  |

|----|-----------------|----------------------------------------------|-----|--|--|

|    | 20.3            | Registers                                    | 161 |  |  |

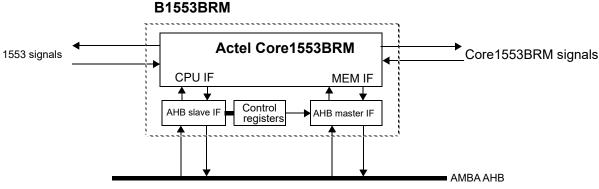

| 21 | MIL-            | -STD-1553B BC/RT/BM                          | 162 |  |  |

|    | 21.1            | Overview                                     | 162 |  |  |

|    | 21.2            | AHB interface                                | 163 |  |  |

|    | 21.3            | 1553 Clock generation                        | 163 |  |  |

|    | 21.4            | Registers                                    | 164 |  |  |

|    | 21.5            | Signal definitions                           | 165 |  |  |

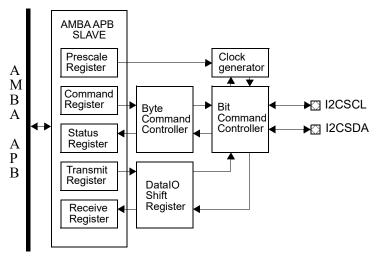

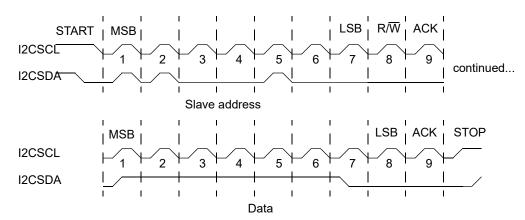

| 22 | I2C-r           | master                                       | 166 |  |  |

|    | 22.1            | Overview                                     | 166 |  |  |

|    | 22.2            | Operation                                    | 166 |  |  |

|    | 22.3            | Registers                                    | 169 |  |  |

|    | 22.4            | Signal definitions                           | 171 |  |  |

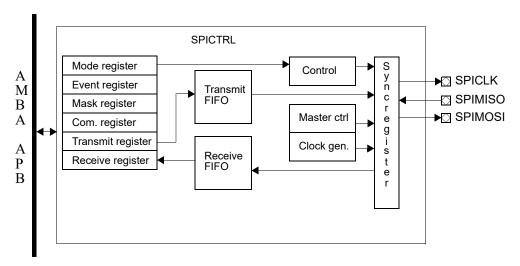

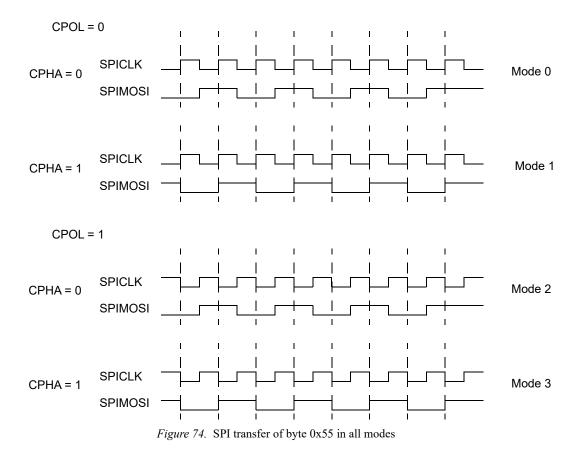

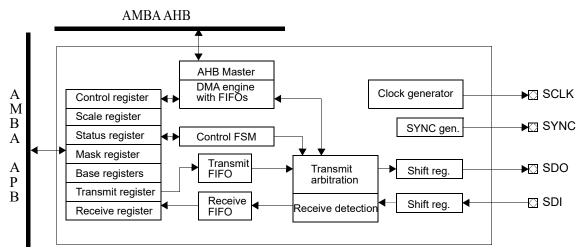

| 23 | SPI C           | Controller                                   | 172 |  |  |

|    | 23.1            | Overview                                     | 172 |  |  |

|    | 23.2            | Operation                                    | 172 |  |  |

|    | 23.3            | Registers                                    | 174 |  |  |

|    | 23.4            | Signal definitions                           | 177 |  |  |

| 24 | SLIN            | K Serial Bus Based Real-Time Network Master  | 178 |  |  |

|    | 24.1            | Overview                                     | 178 |  |  |

|    | 24.2            | Operation                                    | 178 |  |  |

|    | 24.3            | Registers                                    | 181 |  |  |

|    | 24.4            | Signal definitions                           | 185 |  |  |

| 25 | ASCS Controller |                                              |     |  |  |

|    | 25.1            | Overview                                     | 186 |  |  |

|    | 25.2            | Operation                                    | 186 |  |  |

|    | 25.3            | Registers                                    | 187 |  |  |

|    | 25.4            | Signal definitions                           | 188 |  |  |

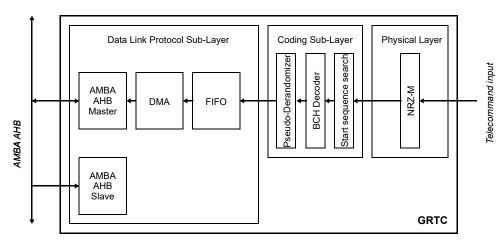

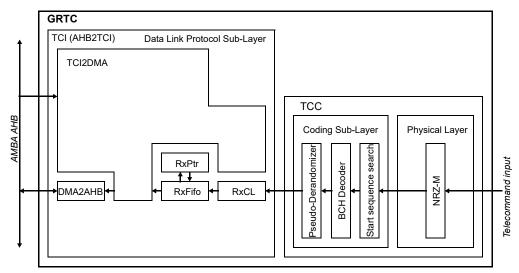

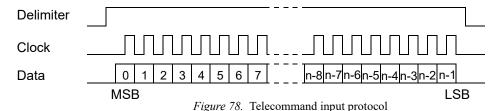

| 26 | GRT             | C - Telecommand Decoder                      | 189 |  |  |

|    | 26.1            | Overview                                     | 189 |  |  |

|    | 26.2            | Data formats                                 | 190 |  |  |

|    | 26.3            | Coding Layer (CL)                            | 191 |  |  |

|    | 26.4            | Transmission                                 | 193 |  |  |

|    | 26.5            | Relationship between buffers and FIFOs       |     |  |  |

|    | 26.6            | Command Link Control Word interface (CLCW)   |     |  |  |

|    | 26.7            | Configuration Interface (AMBA AHB slave)     |     |  |  |

|    | 26.8            | Miscellaneous                                |     |  |  |

|    | 26.9            | Registers                                    |     |  |  |

|    | 26.10           | Signal definitions                           | 207 |  |  |

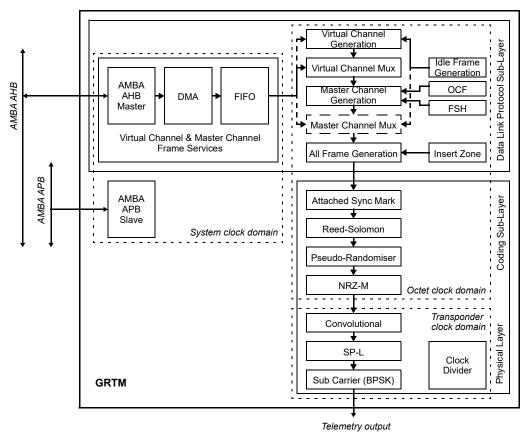

| 27 | GRT.            | M - CCSDS Telemetry Encoder                  | 208 |  |  |

|    | 27.1            | Overview                                     |     |  |  |

|    | 27.2            | References                                   |     |  |  |

|    | 27.3            | Layers                                       |     |  |  |

|    | 27.4            | Data Link Protocol Sub-Layer                 |     |  |  |

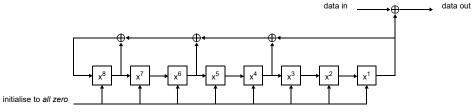

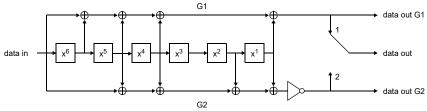

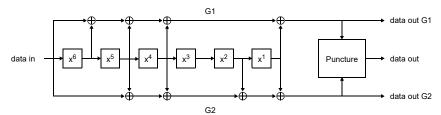

|    | 27.5            | Synchronization and Channel Coding Sub-Layer | 213 |  |  |

## GR712RC

|    | 27.6  | Physical Layer     | 216 |

|----|-------|--------------------|-----|

|    |       | Connectivity       |     |

|    |       | Operation          |     |

|    |       | Registers          |     |

|    |       | Signal definitions |     |

| 28 | Clock | Gating Unit        | 227 |

|    | 28.1  | Overview           | 227 |

|    | 28.2  | Operation          | 227 |

|    |       | Registers          |     |

#### 1 Introduction

### 1.1 Scope

This document is a user's manual for the radiation-hard GR712RC Dual-Core LEON3FT SPARC V8 processor. The GR712RC is based on the LEON3FT and other IP cores from the GRLIB IP library, implemented with the Ramon.Space RadSafe<sup>TM</sup> 180 nm cell library on Tower Semiconductor's 180 nm CMOS process.

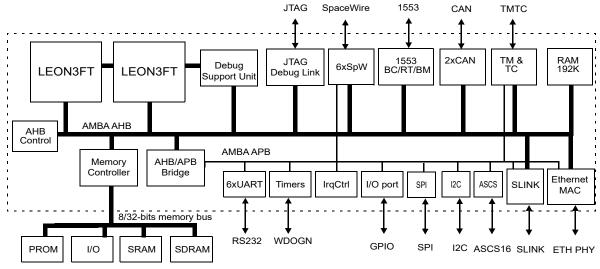

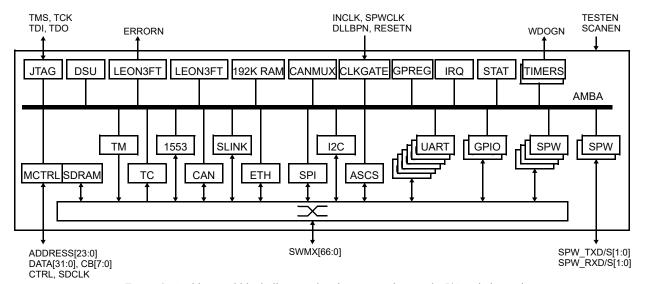

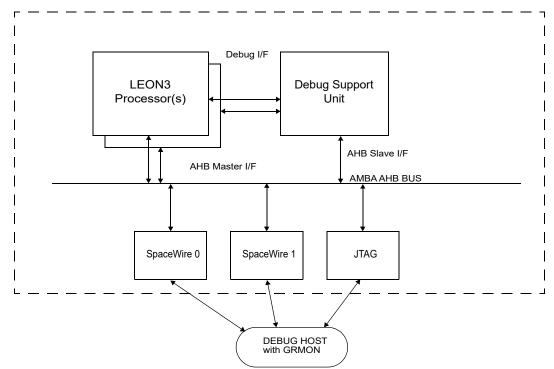

#### 1.2 GR712RC Architecture

The GR712RC has the following on-chip features:

- 2 x LEON3FT processor cores with 32 KiB cache and 32-entry TLB SRMMU

- 2 x Double-precision high-performance floating-point units (GRFPU V2)

- Debug Support Unit (DSU) with 256-line instruction and AMBA AHB trace buffers

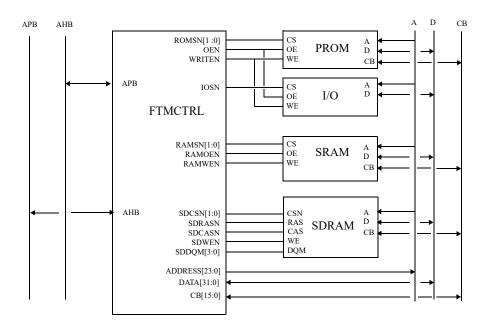

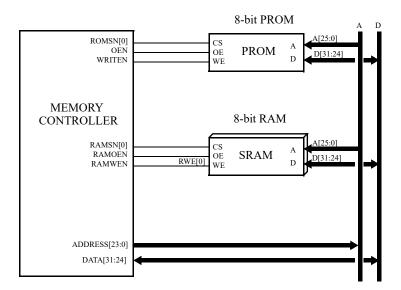

- PROM/SRAM/SDRAM memory controller with BCH and Reed-Solomon error-correction

- up to 32 MiB PROM over two 16 MiB banks

- up to 32 MiB SRAM over two 16 MiB banks

- up to 1 GiB SDRAM over two 512 MiB banks

- 192 KiB on-chip RAM with BCH error-correction (uncacheable)

- 6 x SpaceWire links (two with RMAP support, one DMA channel per link, one port per link)

- 6 x UARTs

- 6 x General Purpose Timers (2 with time latch capability)

- Multi-processor Interrupt Controller with support for 31 interrupts

- 2 x 32 bits General Purpose I/O

- · JTAG debug link

- 10/100 Ethernet MAC with RMII interface

- MIL-STD-1553B BC/RT/BM controller

- 2 x CAN 2.0 controller

- High-speed CCSDS Telecommand decoder and Telemetry encoder

- SPI master controller

- I2C master controller

- SLINK and ASCS16 controllers

- · Clock gating unit

- I/O switch matrix

GR712RC Block diagram

## 1.3 Memory map

The memory map of the internal AHB/APB buses is specified as shown below.

TABLE 1. Internal memory map

| Core                       | Address range                                                                 |                                          | Bus        |

|----------------------------|-------------------------------------------------------------------------------|------------------------------------------|------------|

| FTMCTRL                    | 0x00000000 - 0x20000000<br>0x20000000 - 0x40000000<br>0x40000000 - 0x80000000 | PROM area<br>I/O area<br>SRAM/SDRAM area | АНВ        |

| APBCTRL - 1                | 0x80000000 - 0x80100000                                                       | APB bridge                               | AHB        |

| FTMCTRL                    | 0x80000000 - 0x80000100                                                       | Registers                                | APB        |

| APBUART - 0                | 0x80000100 - 0x80000200                                                       | Registers                                | APB        |

| IRQMP                      | 0x80000200 - 0x80000300                                                       | Registers                                | APB        |

| GPTIMER                    | 0x80000300 - 0x80000400                                                       | Registers                                | APB        |

| SPICTRL                    | 0x80000400 - 0x80000500                                                       | Registers                                | APB        |

| CANMUX                     | 0x80000500 - 0x80000600                                                       | Registers                                | APB        |

| GRGPREG                    | 0x80000600 - 0x80000700                                                       | Registers                                | APB        |

| GRASCS                     | 0x80000700 - 0x80000800                                                       | Registers                                | APB        |

| GRSLINK                    | 0x80000800 - 0x80000900                                                       | Registers                                | APB        |

| GRGPIO - 1                 | 0x80000900 - 0x80000A00                                                       | Registers                                | APB        |

| GRGPIO - 2                 | 0x80000A00 - 0x80000B00                                                       | Registers                                | APB        |

| GRTM                       | 0x80000B00 - 0x80000C00                                                       | Registers                                | APB        |

| I2CMST                     | 0x80000C00 - 0x80000D00                                                       | Registers                                | APB        |

| CLKGATE                    | 0x80000D00 - 0x80000E00                                                       | Registers                                | APB        |

| GRETH                      | 0x80000E00 - 0x80000F00                                                       | Registers                                | APB        |

| AHBSTAT                    | 0x80000F00 - 0x80001000                                                       | Registers                                | APB        |

| APB1 plug&play             | 0x800FF000 - 0x80100000                                                       | Plug&play configuration                  | APB        |

| APBCTRL - 2                | 0x80100000 - 0x80200000                                                       | APB bridge                               | AHB        |

| APBUART - 1                | 0x80100100 - 0x80100200                                                       | Registers                                | APB        |

| APBUART - 2                | 0x80100200 - 0x80100300                                                       | Registers                                | APB        |

| APBUART - 3                | 0x80100300 - 0x80100400                                                       | Registers                                | APB        |

| APBUART - 4                | 0x80100400 - 0x80100500                                                       | Registers                                | APB        |

| APBUART - 5                | 0x80100500 - 0x80100600                                                       | Registers                                | APB        |

| GRTIMER                    | 0x80100600 - 0x80100700                                                       | Registers                                | APB        |

| GRSPW2 - 0                 | 0x80100800 - 0x80100900                                                       | Registers                                | APB        |

| GRSPW2 - 1                 | 0x80100900 - 0x80100A00                                                       | Registers                                | APB        |

| GRSPW2 - 2                 | 0x80100A00 - 0x80100B00                                                       | Registers                                | APB        |

| GRSPW2 - 3                 | 0x80100B00 - 0x80100C00                                                       | Registers                                | APB        |

| GRSPW2 - 4                 | 0x80100C00 - 0x80100D00                                                       | Registers                                | APB        |

| GRSPW2 - 5                 | 0x80100D00 - 0x80100E00                                                       | Registers                                | APB        |

| APB2 plug&play             | 0x801FF000 - 0x80200000                                                       | Plug&play configuration                  | APB        |

| DSU3                       | 0x90000000 - 0xA0000000                                                       | Registers                                | AHB        |

| FTAHBRAM                   | 0xA0000000 - 0xA0100000<br>0x80100000 - 0x80100100                            | RAM area<br>Registers                    | AHB<br>APB |

| B1553BRM                   | 0xFFF00000 - 0xFFF01000                                                       | Registers                                | AHB        |

| GRTC                       | 0xFFF10000 - 0xFFF10100                                                       | Registers                                | AHB        |

| Proprietary, do not access | 0xFFF20000 - 0xFFF20100                                                       | Registers                                | AHB        |

| CANOC                      | 0xFFF30000 - 0xFFF31000                                                       | Registers                                | AHB        |

| AHB plug&play              | 0xfffff000 - 0xfffffff                                                        | Plug&play configuration                  | AHB        |

| prograpmy                  | January Chilinian                                                             | 1 ingespin, configuration                |            |

Access to addresses outside the ranges described above returns an AMBA AHB error response.

## 1.4 Interrupts

The following table specifies the interrupt assignment for the GR712RC.

TABLE 2. Interrupt assignment

| Core                  | Interrupt # | Function                                           |

|-----------------------|-------------|----------------------------------------------------|

| AHBSTAT               | 1           | AHB bus error and EDAC correctable error interrupt |

| APBUART - 0           | 2           | UART1 RX/TX interrupt                              |

| GRGPIO - 1 to 2       | 1-15        | External I/O interrupt (3 & 4 are GPIO only)       |

| CANOC                 | 5-6         | OCCAN interrupt (core 1 - 2)                       |

| GRTIMER               | 7           | GRTIMER timer underflow interrupt                  |

| GPTIMER               | 8-11        | GPTIMER timer underflow interrupts                 |

| IRQMP                 | 12          | IRQMP extended interrupt                           |

| SPICTRL, SLINK        | 13          | SPI and SLINK interrupt                            |

| B1553BRM, GRETH, GRTC | 14          | 1553, Ethernet, and Telecommand interrupt          |

| ASCS                  | 16          | ASCS interrupt                                     |

| APBUART - 1to 5       | 17-21       | UART2-6 RX/TX interrupt                            |

| GRSPW2 - 0 to 5       | 22-27       | SpaceWire 0-5 RX/TX data interrupt                 |

| I2CMST                | 28          | I2C master interrupt                               |

| GRTM                  | 29          | Telemetry encoder interrupt                        |

|                       | 30          | Telemetry encoder time strobe interrupt            |

The interrupts are routed to the IRQMP interrupt controller and forwarded to the LEON3FT processors. Interrupt 16-31 are generated as interrupt 12 and for those interrupts a chained interrupt handler is used.

### 1.5 GRLIB IP cores

The GR712RC uses the following cores from the GRLIB IP library:

TABLE 3. Used IP cores

| Core                                                  | Function                                 | Vendor ID | Device ID |

|-------------------------------------------------------|------------------------------------------|-----------|-----------|

| LEON3FT                                               | Fault tolerant SPARC V8 32-bit processor | 0x01      | 0x053     |

| DSU3                                                  | Debug support unit                       | 0x01      | 0x004     |

| IRQMP                                                 | Interrupt controller                     | 0x01      | 0x00D     |

| APBCTRL                                               | AHB/APB Bridge                           | 0x01      | 0x006     |

| FTMCTRL                                               | 8/32-bit Memory controller with EDAC     | 0x01      | 0x054     |

| AHBSTAT                                               | AHB failing address register             | 0x01      | 0x052     |

| FTAHBRAM                                              | Fault tolerant on chip memory            | 0x01      | 0x050     |

| AHBJTAG                                               | JTAG/AHB debug interface                 | 0x01      | 0x01C     |

| GRSPW2                                                | SpaceWire link with DMA                  | 0x01      | 0x029     |

| B1553BRM                                              | MIL-STD1553B BC/RT/BM controller         | 0x01      | 0x072     |

| CANOC                                                 | OC CAN controller                        | 0x01      | 0x019     |

| GRETH                                                 | 10/100 Ethernet MAC                      | 0x01      | 0x01D     |

| APBUART 8-bit UART with FIFO                          |                                          | 0x01      | 0x00C     |

| GPTIMER Modular timer unit                            |                                          | 0x01      | 0x011     |

| GRTIMER Modular timer unit with time latch capability |                                          | 0x01      | 0x038     |

| GRGPIO General purpose I/O port                       |                                          | 0x01      | 0x01A     |

| GRTC CCSDS Telecommand Decoder                        |                                          | 0x01      | 0x031     |

| GRTM                                                  | CCSDS Telemetry Encoder                  | 0x01      | 0x030     |

| -                                                     | Proprietary                              | 0x01      | 0x080     |

| CANMUX                                                | CAN bus multiplexer                      | 0x01      | 0x081     |

| GRASCS                                                | ASCS16 controller                        | 0x01      | 0x043     |

| GRSLINK                                               | SLINK controller                         | 0x01      | 0x02F     |

| SPICTRL                                               | SPI controller (master only)             | 0x01      | 0x02D     |

| I2CMST                                                | I2C master                               | 0x01      | 0x028     |

| CLKGATE                                               | Clock gating unit                        | 0x01      | 0x02C     |

| GRGPREG                                               | General purpose register                 | 0x01      | 0x087     |

### 1.6 References

| [DS]      | GR712RC - Dual-Core LEON3FT SPARC V8 Processor, Data Sheet, GR712RC-DS, Issue 2.5, Nov 2023, Frontgrade Gaisler, www.frontgrade.com/gaisler                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [SPARC]   | The SPARC Architecture Manual, Version 8, Revision SAV080SI9308, SPARC International Inc.                                                                                                           |

| [JTAG]    | IEEE Standard Test Access Port and Boundary-Scan Architecture, IEEE Std 1149.1-2001                                                                                                                 |

| [SPW]     | ECSS - Space Engineering, SpaceWire - Links, Nodes, Routers and Networks, ECSS-E-ST-50-12C, 31 July 2008                                                                                            |

| [RMAPID]  | ECSS - Space Engineering, SpaceWire Protocol Identification, ECSS-E-ST-50-51C, February 2010                                                                                                        |

| [RMAP]    | ECSS - Space Engineering, Remote Memory Access Protocol, ECSS-E-ST-50-52C, February 2010                                                                                                            |

| [1553BRM] | Core1553BRM Product Handbook, 50200040-0/11-04, November 2004, Actel Corporation                                                                                                                    |

|           | Core1553BRM MIL-STD-1553 BC, RT, and MT, 51700052-4/12.05, v 5.0, December 2005, Actel Corporation                                                                                                  |

|           | Core1553BRM User's Guide, 50200023-0/06.04, June 2004, Actel Corporation                                                                                                                            |

|           | Core1553BRM v2.16 Release Notes, 51300019-8/6.06, June 2006, Actel Corporation                                                                                                                      |

| [MMU]     | Technical Note on LEON SRMMU Behaviour, GRLIB-TN-0002, Issue 1, Revision 1, February 2015, Frontgrade Gaisler, www.frontgrade.com/gaisler                                                           |

| [GRETH]   | Technical Note on GRETH Controller Behaviour, GRLIB-TN-0008, Issue 1, October 2015, Frontgrade Gaisler, www.frontgrade.com/gaisler                                                                  |

| [TN0009]  | Technical Note on Stale Cache Entry After Store with Data Tag Parity Error, GRLIB-TN-0009, Issue 1, September 2016, Frontgrade Gaisler, www.frontgrade.com/gaisler                                  |

| [TN0011]  | Technical Note on LEON3/FT AHB Lock Release during Atomic Operation, GRLIB-TN-0011, Issue 1, November 2017, Frontgrade Gaisler, www.frontgrade.com/gaisler                                          |

| [TN0012]  | Technical Note on GR712RC Incorrect Annulation of Floating-point Operation on Instruction Cache Parity Error, GRLIB-TN-0012, Issue 1, November 2017, Frontgrade Gaisler, www.frontgrade.com/gaisler |

| [TN0013]  | Technical Note on GRFPU Floating-point controller: Missing FDIV/FSQRT Result, GRLIB-TN-0013, Issue 1, November 2017, Frontgrade Gaisler, www.frontgrade.com/gaisler                                 |

| [AN0003]  | FTMCTRL: BCH EDAC with multiple 8-bit wide PROM and SRAM banks, GRLIB-AN-0003, Issue 1, April 2017, Frontgrade Gaisler, www.frontgrade.com/gaisler                                                  |

| [TN0018]  | Technical Note on LEON3FT RETT Restart Errata, GRLIB-TN-0018, Issue 1, January 2020, Frontgrade Gaisler, www.frontgrade.com/gaisler                                                                 |

| [TN0002]  | Technical Note on GR712RC memory production test coverage and usage constraints, GR712RC-TN-0002, Issue 1.1, September 2022, Frontgrade Gaisler, www.frontgrade.com/gaisler                         |

| [TN0020]  | Technical Note on FTMCTRL/MCTRL/SDCTRL: SDRAM Initialization Errata, GRLIB-TN-0020, Issue 1, September 2022, Frontgrade Gaisler, www.frontgrade.com/gaisler                                         |

#### 1.7 Errata

#### 1.7.1 FTAHBRAM: On-chip Memory not cacheable

The 192 KiB on-chip memory at address 0xA00000000 is not cacheable in the L1 caches of the processors.

See sections 4.2.17 and 6.1 for details.

#### 1.7.2 CAN OC: interrupt can be cleared before read

The Transmit Interrupt can be cleared before read, if a read access is made to the Interrupt Register in the same clock cycle as the interrupt is set by the transmitter logic.

Instead of looking at the Transmit Interrupt flag, the Transmit Buffer Status flag in the Status Register can bee looked at when something has been scheduled for transmission.

See section 18.4.5.

#### 1.7.3 GRSPW2: interrupt can be lost

If an AMBA AHB error occurs in the same clock cycle as a SpaceWire link error or Time-Code Tick-Out interrupt is generated and the AMBA AHB error interrupts are disabled then the corresponding interrupt will be lost (i.e. SpaceWire link error or Time-Code Tick-Out interrupt)

The workaround is to also enable the AMBA AHB error interrupt when any of the link error or Time-Code Tick-Out interrupts are enabled. An AMBA AHB error interrupt will cause the corresponding DMA channel to stop, and therefore interrupt handling will be required anyway.

See section 16.9.

#### 1.7.4 GRSPW2: CRC calculation partially incorrect

RMAP CRC calculation for the DMA receiver does not work correctly under all conditions. The detected header length is not used correctly in cases when two characters are received on consecutive cycles and one of them is the header CRC. This results in an incorrect header CRC indication in the receiver descriptor (i.e. Header CRC (HC) field). The calculation is continued however (as described in the manual) and the data CRC indication (i.e. Data CRC (DC) field) is still correct and covers the whole packet and can thus be used to determine that there are no errors in the complete packet.

See section 16.4.5.

#### 1.7.5 SPICTRL: transfers in progress bit not cleared

The Transfer in Progress bit (TIP the core's Event Register is not cleared automatically by the core if an overrun occurs. The core needs to be disabled in order to clear the bit. The problem does not affect most software drivers.

Workaround 1: Read receive queue so that no overrun occurs.

**Workaround 2**: Disable and re-enable core if overrun occurs.

**Workaround 3**: Do not use Transfer in Progress (TIP) interrupts.

See section 23.3.

#### 1.7.6 SPICTRL: back-to-back transfers

Back-to-back transfers where a word is written to the core's transmit queue at the very end of the transfer of a previous word may cause the core to essentially change the clock phase (CPHA) of the SPI communication. This leads to transmission and reception of wrong data.

The SPI controller regards a transfer as completed when the last bit has been sampled. With clock phase 1 there is a window between sampling of the last bit and when the SCK clock line returns to its idle state. If a new transfer is started (a word is written to the core's transmit queue) in this window, then the bug will be triggered.

This scenario can occur when writing a series of words to the SPI controller and the delay between two writes matches the time it takes for the core to transfer the current transmit queue contents. A possible scenario is that a processor wants to send two words over SPI, after the first word has been writ-

ten the processor gets an interrupt, when the processor returns from serving the interrupt and writes the second word the second write could hit the window.

Software drivers that use SPI clock phase 0 (data sampling starts on the first transition of SCK) are potentially affected.

Workaround 0: Use a SPI clock phase of 1 and adjust the CPOL value instead.

Workaround 1: Ensure that all words of a transfer are written to the transmit queue before the last bit of a preceding word has been sent.

See section 23.3.

#### 1.7.7 FTMCTLR: EDAC usage with 8-bit wide memory

When multiple SRAM or PROM memory banks are used in 8-bit mode with EDAC, the configured bank size must be set to at least four times the actual device size.

Refer to [AN0003] for further details.

#### 1.7.8 LEON3FT Cache Controller: Incorrect Bus Access After Power-Down

A LEON3 with support for clock gating has one clock that is kept running and one clock that is gated off in power-down mode. Due to a design error in the LEON3 version implemented in the GR712RC, the gated clock is used for logic that keeps track of the state of the AMBA bus. Due to this error, the first bus access made after leaving power-down may be performed incorrectly.

An incorrect bus access will be made under the following conditions:

- 1. A processor enters power-down mode while it has received grant to the bus.

- 2. The processor leaves power-down while another master is making a bus access.

- 3. The processor leaving power-down mode itself starts a bus access before the access of the other master finishes.

If the above conditions are fulfilled then the first bus access made by the processor as it leaves powerdown mode will be performed incorrectly. In case of a read-access, invalid data will be returned. In case of a write-access the write may not complete correctly as seen by a bus slave.

The processor makes bus accesses in the following circumstances:

- 1. In response to store-instructions.

- 2. In response to load-instructions in case of data cache misses.

- 3. Instruction fetches in case of instruction cache misses.

- 4. If the MMU is enabled, table walks are made in case of TLB misses.

The GR712RC AMBA bus uses round-robin arbitration and a bus master that has received grant of the bus will keep the grant until another master requests bus access. Conditions 1 and 2 are therefore expected to be fulfilled often in applications involving power-down and use of DMA or both CPUs. Whether or not condition 3 is fulfilled depends sensitively on the instruction sequence following the power-down instruction.

#### **Workaround 1**: Do not use power-down

The issues described in this section are avoided by not entering power-down mode. Refrain from using the wr %asr19 sequence.

**Workaround 2**: Keep instruction cache enabled, execute power-down sequence from cacheable memory, make a controlled bus access whose data is discarded.

Note that the FTAHBRAM is not cachable (see section 1.7.1) and therefore the power-down instruction should never be executed from the FTAHBRAM.

When executing from cacheable memory with the instruction cache enabled, the sequence below is immune to the errata:

```

__asm___volatile__(

".align 32\n"

"mov %%g0, %%asr19\n"

"lda [%0] 0x1C, %%g0\n"

".align 32\n"

:

: "r"(0xfffffff0));

```

The write to %asr19, the load, and the three following instructions, are all guaranteed to be in the I-cache when the processor leaves power-down mode. The load instruction bypasses the MMU and cache which guarantees that a bus access will be made without side effects on register or cache contents. Once the load completes, the state of the cache controller AHB interface will be consistent with the state of the AHB bus.

Due to pipeline delays, a branch or jump instruction placed just after a load instruction can result in an instruction fetch to the target of the branch being executed on the bus before the preceding load. The ".align 32" directive forces any following jump or branch instruction to be placed far enough away from the load instruction to prevent this.

In case of coming out of power-down mode due to a pending interrupt, the instruction following the %asr19 access will be executed prior to taking the interrupt trap. And the load will be executed on the bus before trying to fetch the first instruction of the trap handler. So even if the trap handler is not currently in cache, the load will occur before fetching it.

Note that no workaround can be fully immune to the errata in the presence of SEUs. If, while the CPU is powered down, an SEU occurs in the instruction cache line containing the power-down instruction itself, then this will force the cache controller to issue an instruction fetch as it comes out of power-down. This instruction fetch will be executed before the load instruction and may therefore return invalid data.

#### Software packages with workarounds:

The Frontgrade Gaisler provided run time environments, from versions shown below, have integrated a workaround for the data cache for this bug. The software is assumed to be run with cache enabled (default behaviour in bootladers) and from cacheable memory and does not include any workaround for the instruction cache, since this is not required with these assumptions.

| BCC1 (bare-C) Not applicable, does not use power-down instruction |                                                                                                                                                                                                                                        |  |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BCC2                                                              | Workaround included in all releases. The workaround assumes that the MMU remains disabled.                                                                                                                                             |  |

|                                                                   | The power-down instruction will only be emitted if user code explicitly calls the function bcc_powerdown(). BCC2 will never enable the MMU.                                                                                            |  |

| Linux                                                             | Partial workaround since 2.6.21 (SnapGear p42). In mainline since 2.6.39.                                                                                                                                                              |  |

|                                                                   | And update is planned for 5.10-1.6.                                                                                                                                                                                                    |  |

|                                                                   | All 2.6.36 releases and later that have been distributed via Frontgrade Gaisler.                                                                                                                                                       |  |

| RCC (RTEMS)                                                       | RCC-1.2.x based on RTEMS-4.10 and later. RCC-1.3 based on RTEMS5 uses the same workaround. This workaround assumes that the MMU remains disabled.                                                                                      |  |

|                                                                   | Since RCC-1.3.2 the workaround allows the MMU to be enabled. RTEMS itself does not use the MMU, but one of the sample applications distributed with RCC demonstrates how to set up a static MMU configuration for RTEMS to run inside. |  |

| VxWorks | VxWorks 6.3 and 6.5 are not affected since power-down is not used.                                                     |

|---------|------------------------------------------------------------------------------------------------------------------------|

|         | Partial workaround in 6.7 since release 1.0.3.                                                                         |

|         | Corrected workaround in VxWorks 6.9 v2.2.4 and VxWorks 7 v4.7.                                                         |

| GRBOOT  | Power-down is used in the init_rompark routine which has a partial workaround. An update is planned for version 1.5.2. |

The software versions that are stated to implement partial workarounds all share a potential vulnerability in that the compiler may place a branch or jump instruction close enough to the LDA that an instruction fetch to the branch target address could be performed before the LDA completes. Additionally, the partial workarounds for VxWorks and Linux did not bypass the MMU and this could result in erroneous page table walks in case of a TLB miss.

#### 1.7.9 Failing SDRAM Access After Uncorrectable EDAC Error

When the memory controller of the GR712RC LEON system detects an uncorrectable EDAC error, it should respond with an AMBA ERROR response and then return to normal operation. Due to an incomplete condition check for starting new SDRAM accesses, the memory controller may perform a read access following an uncorrectable error even if there is no incoming access on the AMBA bus. The result will be discarded unless a AMBA read access to the SDRAM memory area is performed before the SDRAM read operation has finished. The extra read access will not occur if there is a SDRAM refresh operation pending.

The memory controller will return to normal operation after the extra read access has been performed. If a AMBA read is performed to the SDRAM area before this unintended read access has completed then the result of the incoming AMBA read access may be erroneous. The result can be an AMBA ERROR response or the memory controller may deliver data from the wrong memory location without a AMBA ERROR response (note that the first access that read a location which had an uncorrectable error will always receive an AMBA ERROR response).

The erratum can be triggered when:

- The FTMCTRL has been configured with minimum t<sub>RP</sub> SDRAM timing, and

- A read access to SDRAM results in an uncorrectable EDAC error, and

- A second AMBA read access is performed to the SDRAM memory area in the window zero to five system clock cycles after the AMBA ERROR response given due to the uncorrectable EDAC error.

If the incoming read access occurs during the last cycle of the vulnerable window in time then the controller will return data from the memory location of the first access, which will may trigger an AMBA ERROR response if the uncorrectable error remains at that memory location. For incoming accesses during the other cycles in the vulnerable window, the access will malfunction but the data read by the memory controller may still have valid check bits. If the check bits are valid then the erroneous data will be delivered without any AMBA ERROR for the second access.

Uncorrectable SDRAM errors are expected to be a rare occurrence, provided that scrubbing of correctable errors has been implemented in the system.

The uncorrected error response may be the result of a processor access which leads to the processor taking a trap. The read of the trap table may then occur during the window when the FTMCTRL performs the extra read access which leads to erroneous data or a AMBA ERROR response when the processor fetches the trap table. In multi-master systems, one master may trigger the uncorrectable error and a second master may perform a read access in the window where the FTMCTRL is malfunctioning.

There are cases where the unintended read access is prevented. A SDRAM command issue or a refresh operation are cases that prevent triggering the erratum.

It is recommended that all GR712RC systems implement the following workaround.

#### Workaround:

The erratum cannot be triggered when the MCFG2.TRP field (bit 30 of MCFG2 register) is set to 1 (SDRAM  $t_{RP}$  parameter is three clock cycles).

VxWorks board support package for GR712RC will be updated to default MCFG2.TRP=1. For other boot loaders, please refer to the software package's documentation for information on how to set MCFG2.TRP.

GRMON2 will be updated to automatically set MCFG2.TRP for GR712RC.

Please contact Frontgrade Gaisler support for information on specific software versions.

#### Other information:

The failure will not occur if the second incoming access is to the PROM, SRAM or IO area. The memory controller may perform the unintended read access to SDRAM but software will not be affected.

The bug does not affect SRAM and PROM areas.

The controller will always perform the unintended SDRAM read access when MCFG2.TRP=0, unless there is a refresh operation pending.

It takes exactly five system clock cycles after the AMBA ERROR response until the memory controller is back in normal state.

#### 1.7.10 MIL-STD-1553B core duplicate interrupt assertion

Under certain conditions interrupts from the MIL-STD-1553B core can appear to be duplicate. The Interrupt Pending status bit in the Multiprocessor Interrupt Controller might be asserted an extra time after the interrupt event is successfully processed. The problem appears more frequently with a higher ratio of the AHB system bus frequency to the MIL-STD-1553B core frequency, but can be present for any combination thereof. A possible consequence of this problem is that the Interrupt Service Routine associated with the MIL-STD-1553B core, IRQ 14, gets called twice.

The reason for this spurious behavior lies in how the Actel Core1553BRM controller propagates the IRQ to the interrupt controller. The IRQ line is propagated from the Interrupt Request pulse from the Core1553BRM and is re-synchronized into the system clock domain and fed as an IRQ source to the interrupt controller. Assuming, for instance, an AHB system bus frequency four times higher than the MIL-STD-1553B core frequency, since the Interrupt Request line output of the Core1553BRM is high for 3 cycles when INTLEVEL=0, this will result in a 12 cycle pulse coming in to the interrupt controller. When this pulse is longer than it takes for the CPU to handle the interrupt, this will lead to a second interrupt being stored into the interrupt controller, and this will then cause the interrupt handler to be called twice.

#### Workaround:

A possible workaround is to manually clear the interrupt pending status in the IRQ handler via the Interrupt Clear Register of the IRQ controller. This assumes that there are no other other sources (hardware or software) that can assert interrupt 14. This needs to be done early, before reading the BRM IRQ status/log to eliminate the risk of losing any IRQ events from the BRM.

The other workaround is simply to accept the extra IRQs and make the IRQ handler capable of handling this case.

#### 1.7.11 Technical Note on LEON SRMMU Behaviour

The MMU behavior when updating the FSR and FAR registers in this device does not fully comply to the SPARC V8 Manual. Special care should be taken by users that utilize the MMU. This is addressed in Linux release 3.10.58-1.0.4 and onwards. Other users who implement MMU handling should consult [MMU] for further information.

#### 1.7.12 Technical Note on GRETH Ethernet Controller Behaviour

The state in which the GRETH receiver control finite state machine discards packets does not take overrun into account in all cases. The discard state is entered when a received packet is determined to be dropped. The size of the packet is checked and that amount of data is read from the FIFO. When an overrun has occurred, the amount written to the FIFO is not the same as the length of the packet and in those cases the FIFO should be emptied completely. This was not done if:

- 1 The packet in question had a MAC address which the core should not receive, or

- 2 if the receiver was enabled when the packet was received but the descriptor was not enabled and the descriptor read was so slow that an overrun occurred during that time.

These conditions cause the Ethernet receiver to hang. No further traffic can be received and the GRETH must receive a hardware reset to recover. This hardware reset can be attained by either reseting the whole device or by forcing a GRETH reset via the clock gating unit (see chapter 28 in this document).

#### Workaround:

As described in the previous section, the problem occurs under two conditions. The first condition can be avoided by enabling promiscuous mode for the Ethernet controller. This mode is enabled via the GRETH control register. Promiscuous mode may lead to additional software load of the systems since more packets may need to be processed. In applications where the GRETH is used in a limited network with few members, the addition of promiscuous mode should have less negative effects.

Use of switches instead of hubs in the network since the GRETH controller will in this case receive fewer packets with MAC addresses that will be discarded.

The second trigger condition is system and application specific. The condition is not expected to happen in systems like the GR712RC. Other systems with memory controllers that have high latency and systems that introduce several bridges between the GRETH controller and main memory may encounter condition 2.

There is no status bit in the controller that will indicate that the receiver has hanged. The condition can be detected by the Ethernet controller no longer receiving any packets. This could require implementation at a higher level of a heart beat function so that system software can detect that packets are missing and correct the situation. The only way to correct the condition is to perform a hardware reset of the GRETH controller. The soft reset functionality that can be triggered via the GRETH control register is not enough to resolve the receiver hang.

Users of the GRETH Ethernet Controller should consult [GRETH] for further information and updates.

#### 1.7.13 Technical Note on Stale Cache Entry After Store with Data Tag Parity Error

Under certain conditions, a data coherency issue can occur when the processor has executed a back-to-back store operation and the first store's address hits a cache set that has a data cache tag parity error. The second store operation successfully stores its data content into the main memory but the data cache controller fails to update the old data in the data cache with the new data from the store operation. This leads to an incoherent state, data in the data cache is not the same as in the main memory. A subsequent read from the second location will get the old data instead of the new data if the data cache line is still valid in the cache.

Refer to [TN0009] for further details and workaround.

#### 1.7.14 Never disable the TLB when the MMU is enabled

When the MMU is enabled but TLB disabled, the MMU can in certain cases perform incorrect address translation. Therefore it is advised to never set the TLB disable bit in the MMU control register. The TLB disable bit is not set by any operating system provided by Frontgrade Gaisler.

#### 1.7.15 Technical Note on LEON3/FT AHB Lock Release During Atomic Operation

In certain cases, where the MMU is enabled, a LEON3/FT core can lose the bus lock before completing the store operation required by an atomic instruction (swap, ldstub, casa). The atomic instruction will complete atomically in terms of instruction order but due to losing bus lock before store, the atomicity on the bus level is not guaranteed. As a result, if before being able to make the store required by the atomic instruction, if another master gains access to the bus and makes a store to the same address (used by the atomic instruction) it may cause erroneous behavior since atomicity is lost.

Refer to appendix [TN0011] for further details and workaround.

# 1.7.16 Technical Note on GR712RC Incorrect Annulation of Floating-point Operation on Instruction Cache Parity Error

In certain cases, an incorrect update of a floating point register or floating-point condition register due to execution and commit of an extra floating point instruction outside of the correct instruction flow can occur. This can in turn cause erroneous behavior of software. The error can occur when there is a tag or data parity error in the instruction cache.

Refer to [TN0012] for further details and workaround.

#### 1.7.17 Technical Note on GRFPU Floating-point controller: Missing FDIV/FSQRT Result

This document describes a corner case present in the GRFPC floating point controller, which is the hardware used to interface the GRFPU floating point unit with the LEON3/FT and LEON4/FT processors. The corner case described in this document can cause a FDIV/FSQRT operation result not to be committed to the floating point register file. The issue manifests if;

- · two instructions exist in the instruction flow between two FDIV/FSQRT instructions, and

- at least one of them is a floating point operation, and

- the processor encounters certain number of hold cycles after the first FDIV/FSQRT operation reaches execute stage of the pipeline.

Refer to [TN0013] for further details and workaround.

#### 1.7.18 Don't break into debug mode on RETT instructions

Avoid breaking into debug mode on RETT instructions because this causes incorrect behavior when resuming.

#### 1.7.19 Stores to ASI 0x1C may update data cache

When a store is made using the store-alternate instruction with the address space identifier set to MMU/cache bypass (STA with ASI set to 0x1C), the processor's data cache controller handles this as if it was a regular store instruction with the same address and data. This may lead to unexpected data cache updates.

This is particularly an issue when the MMU is enabled and used for virtual-to-physical address translation. In this case, the given store address is used as a physical address when written to memory, as intended, but gets used as a virtual address in the cache update.

It is recommended that applications avoid using stores with ASI 0x1C and reimplement such code using ordinary store instructions instead. Alternatively, a data cache flush can be used to get a consistent cache state after STA ASI=0x1C instructions have been performed (however note that traps occurring between the STA and the flush may see the invalid cache state).

#### 1.7.20 Technical Note on LEON3FT RETT Restart Errata

The document describes an errata for the LEON3FT processor for a corner case requiring both a trap handler returning to a specific instruction, and a radiation induced upset in a specific location in the instruction cache memory, to occur close in time to each other. The likelihood of triggering the errata is application dependent, but is under typical application scenarios very low.

Refer to [TN0018] for further details and workaround.

#### 1.7.21 FTAHBRAM: Data corruption when using back-to-back writes

Data errors can be induced in memory when the FTAHBRAM is written using back-to-back writes. Refer to [TN0002] for further details.

In the first revision of [TN0002], only burst writes were mentioned. However, from the point of view of the FTAHBRAM, this is equivalent to back-to-back word writes. In this context, a back-to-back write is defined as taking place when two AHB writes occur during two consecutive clock cycles. This happens during write bursts of length 2 or more. Additionally, since the FTAHBRAM has 0 write waitstates (see table 34), back-to-back writes can occur when two AHB masters attempt to write to the FTAHBRAM on the same or neighboring clock cycles. In the GR712RC non-burst back-to-back writes can only occur from near simultaneous writes from at least two AHB masters. For example, a single CPU executing multiple sequential ST-operations will generate at most one AHB write every 2 cycles, hence this does not cause a back-to-back AHB write sequence.

#### Workaround 1:

Do not use the FTAHBRAM.

#### Workaround 2:

Use only single (word, halfword and byte) write accesses and avoid burst write accesses when accessing FTAHBRAM.

This means that store double (STD) operations should not be performed by the processors to the FTAHBRAM and DMA buffers should not be placed in FTAHBRAM. Additionally, only one AHB master at a time may perform word writes to the FTAHBRAM. Simultaneous sub-word writes cannot trigger the error.

An exception is the MIL-STD-1553B interface because its DMA engine only uses half-word memory accesses. This prevents the occurrence of back-to-back writes and allows DMA descriptors and data to be placed in the FTAHBRAM without risk.

#### 1.7.22 Technical Note on FTMCTRL/MCTRL/SDCTRL: SDRAM Initialization Errata

The document describes an errata for the SDRAM memory controller where initialization of external SDRAM may fail, which in turn can lead to SDRAM memory accesses malfunctioning. To ensure proper SDRAM functionality a workaround has to be implemented in software.

Refer to [TN0020] for further details and workaround.

In addition to the SDRAM initialization sequence, LOAD-MODE-REGISTER commands sent via the command field in the MCFG2 register are also affected by the errata.

#### 1.7.23 DSU register area is cacheable

The GR712RC debug support unit (DSU)has an AHB slave interface that occupies the address range 0x9000000-0x9FFFFFFF in AHB address space. Due to a design error, this address range is cacheable by the processors. If a processor performs a load of an address in this range, then the data will be stored in the data cache. Subsequent accesses to the same address will return the cached data instead of reading the register value.

Note that the DSU is not intended to be accessed from the processors itself, but from an external debug host via JTAG or RMAP. Modifying DSU registers from software can lead to undefined behavior in attached debuggers.

#### Workaround 1:

Do not access the DSU from software running in the GR712RC.

#### Workaround 2:

If software on the GR712RC must access the DSU register space, it must bypass the data cache. This can be done with load/store instructions to alternate memory space with ASI=0x1C (bypass cache and MMU).

## 1.8 Document revision history

TABLE 4. Revision history

| Issue | Date       | Sections                 | Description                                                                                                                    |

|-------|------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 2.16  | 2023-11-27 | 1.4, 8.2.3               | Added that AHBSTAT generates interrupt on correctable errors.                                                                  |

|       |            | 1.6                      | Updated [DS] to version 2.5. Added [JTAG].                                                                                     |

|       |            | 1.7.8, 4.2.14            | Recommended workaround changed. Clarified trigger condition.                                                                   |

|       |            | 1.7.12                   | Made description more specific to the GR712RC.                                                                                 |

|       |            | 1.7.21                   | New revision of [TN0002]. Added that DMA buffers for the MIL-STD-1553B interface can be placed in FTAHBRAM despite the errata. |

|       |            | 1.7.22, 5.8.6            | Added that commands sent using MCFG2 are affected by errata.                                                                   |

|       |            | 1.7.23, 4.2.17           | Added errata about DSU register space being cachable.                                                                          |

|       |            | 2, 2.1-2.3               | Divided into subsections to simplify navigation via PDF bookmarks. Mention that input-only pins are not muxed.                 |

|       |            | 2.3                      | Added "condition" to header of Table 9. Changed "control register" to "mode register" in the SPI row.                          |

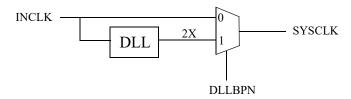

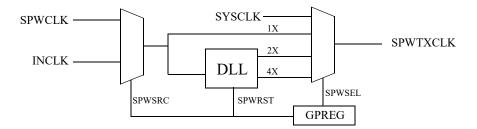

|       |            | 3, 3.1, 3.2, 3.3,<br>3.8 | Replaced MFDLL by DLL, CLK by SYSCLK and "SpaceWire TX clock" by SPWTXCLK. Added cross-references to GPREG.                    |

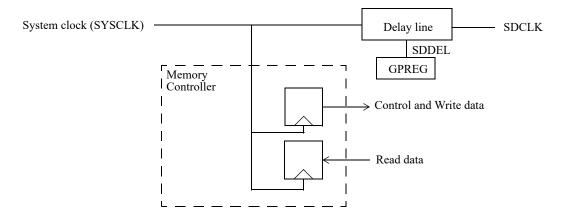

|       |            | 3.8, 13.2                | Changed field name to SDDEL for consistency.                                                                                   |

|       |            | 3.9                      | Added enable conditions for gated clocks in table.                                                                             |

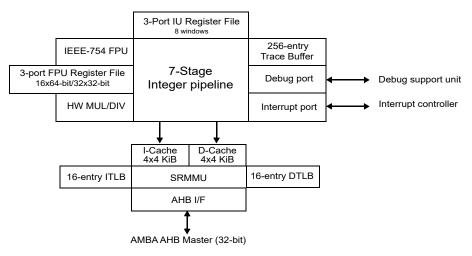

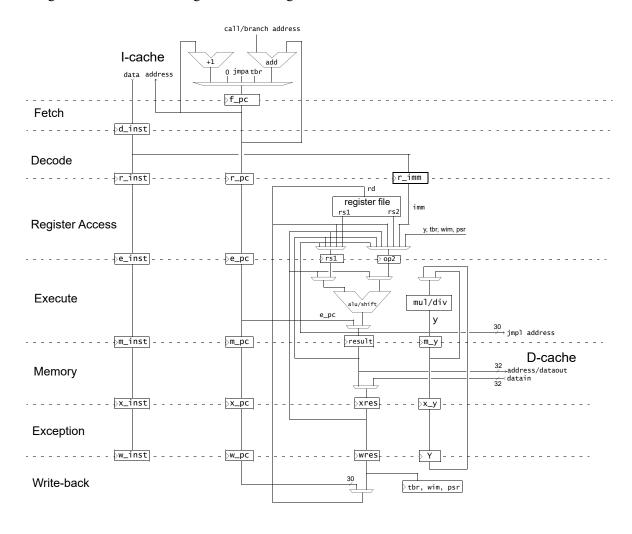

|       |            | 4.1                      | Added size of caches, buffers and register files to block diagram.                                                             |

|       |            | 4.1.2                    | Mentioned the purpose behind bus-snooping.                                                                                     |

|       |            | 4.1.3                    | Changed the word "unique" to "separate".                                                                                       |

|       |            | 4.1.5, 4.1.6,<br>4.2.14  | Added cross-references to other chapters.                                                                                      |

|       |            | 4.2.11                   | Corrected spelling for tt=0x20 and tt=0x2B.                                                                                    |

|       |            | 4.2.12                   | Changed "an" to "a".                                                                                                           |

|       |            | 4.2.13                   | ASI=0x1C bypasses the data cache. Added "diagnostic access".                                                                   |

|       |            | 4.2.15                   | Added interpretative comments on the reset state.                                                                              |

|       |            | 4.2.16                   | Replaced "first/second processor" by "CPU0/1". Added cross-reference to the cache control register.                            |

|       |            | 4.4.1                    | CASA instructions generate locked AHB transfers.                                                                               |

|       |            | 4.6, 4.6.3               | Added references to [SPARC].                                                                                                   |

|       |            | 4.9                      | Added that the CPU1 state has no effect on ERRORN.                                                                             |

|       |            | 5.4                      | Specified that waitstates are added to the data2-phase.                                                                        |

|       |            | 5.5, 5.6, 5.7            | Corrected spelling and grammar.                                                                                                |

|       |            | 5.8.3                    | Merged 5.8.3 with 5.9.5. Added cross-reference to 1.7.22.                                                                      |

|       |            | 5.8.5-5.8.9,<br>5.9-5.14 | The previous section 5.9 is now 5.8.5. This changes the numbering of the subsequent sections from 5.10-5.15 to 5.9-5.14.       |

|       |            | 5.14                     | Added "(bootstrap)" to the Type column in the last two rows.                                                                   |

|       |            | 8.1, 8.2.1, 8.2.2        | Block diagram corrected and moved to 8.1. Added note on pulsed and level interrupts. Wording change on interrupt 15.           |

|       |            | 9.2, 9.6.5               | Added note that DSU registers are accessible from the CPUs. Added information about the time tag, and about timer freeze.      |

|       |            | 9.4                      | Load/store parameters are in bits 95:64.                                                                                       |

TABLE 4. Revision history

| Issue | Date       | Sections                               | Description                                                                                                                               |  |  |  |

|-------|------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2.16  | 2023-11-27 | 9.5                                    | Replaced NWINDOWS by 8 in IU register address formulas.                                                                                   |  |  |  |

|       |            | 10.1, 10.2,<br>10.2.2, 10.2.2,<br>10.4 | Added information about instruction register length, implemented instructions, IDCODE and a note on TDO. Minor changes in wording.        |  |  |  |

|       |            | 11.2                                   | Explained why WDOGN cannot connect to RESETN when the 2xDLL system clocking solution is used.                                             |  |  |  |

|       |            | 11.2, 11.3,<br>12.2, 12.3              | Expanded on the consequences of the shared decrementer.  Added note on the timer freeze function.                                         |  |  |  |

|       |            | 14.1                                   | Input buffers are disabled when output buffers are enabled.                                                                               |  |  |  |

|       |            | 14.2                                   | Some GPIOs are input only. Some do not drive interrupts.                                                                                  |  |  |  |

|       |            | 15.1                                   | Added FIFO size and clock source to the block diagram.                                                                                    |  |  |  |

|       |            | 15.2.2                                 | Corrected description of input filter.                                                                                                    |  |  |  |

|       |            | 15.3                                   | Reformatted baudrate equation.                                                                                                            |  |  |  |

|       |            | 15.6                                   | Added software usage notes on receiver FIFO interrupts.                                                                                   |  |  |  |

|       |            | 16+subsections                         | "GRSPW" changed to "GRSPW2".                                                                                                              |  |  |  |

|       |            | 16.1, 16.3.2,<br>16.3.3, 16.7          | Added information about FIFO sizes and corrected receiver architecture in block diagram. Made use of SYSCLK and SPWTXCLK for consistency. |  |  |  |

|       |            | 16.8                                   | Additional notes on clocking, bitrate and clock recovery.                                                                                 |  |  |  |

|       |            | 16.9                                   | Removed mentions of "SW-node".                                                                                                            |  |  |  |

|       |            | 16.10                                  | Added bootstrap signals to list of signals in table 105.                                                                                  |  |  |  |

|       |            | 21.3                                   | Added that TCLK is not supplied to the Core1553BRM.                                                                                       |  |  |  |

|       |            | 14-19, 21-27                           | Added cross-references to the switch matrix (chapter 2) from "Signal description" subsections.                                            |  |  |  |

|       |            | 16-19, 21, 26,<br>27                   | Added cross-references to the clock gating unit (chapter 28) from the "Overview" subsections.                                             |  |  |  |

| 2.15  | 2022-10-11 | 1.6, 1.7.22                            | Added errata about SDRAM initialization                                                                                                   |  |  |  |

|       |            | 1.7.21                                 | Updated errata about back-to-back writes to FTAHBRAM                                                                                      |  |  |  |

| 2.14  | 2022-03-18 | 1.6                                    | Updated download links for reference documents                                                                                            |  |  |  |

|       |            | 1.7.1, 1.7.21, 6,<br>6.2               | Added errata about burst writes to FTAHBRAM                                                                                               |  |  |  |

| 2.13  | 2020-04-09 | 17.5.1, 17.7                           | Added description of GRETH PHY interrupts                                                                                                 |  |  |  |

|       |            | 1.6, 1.7.20                            | Added errata about RETT restart                                                                                                           |  |  |  |

TABLE 4. Revision history

| Issue | Date       | Sections              | Description                                                                                           |

|-------|------------|-----------------------|-------------------------------------------------------------------------------------------------------|

| 2.12  | 2018-07-19 | 4.5.4                 | Corrected naming of DDE in Cache Control Register field descriptions                                  |

|       |            | 4.5.7                 | Clarified which fields of the Cache Control Register that are 0 after reset                           |

|       |            | 5.10.2                | Corrected code generation polynomial for Reed-Solomon EDAC                                            |

|       |            | 12.3                  | Corrected GRTIMER Configuration register reset value                                                  |

|       |            | 15.5                  | Added note about debug mode in APBUART not being affected by system reset                             |

|       |            | 18.3                  | Corrected address range for CAN core 2                                                                |

|       |            | 18.6                  | Corrected spelling of BasicCan                                                                        |

|       |            | 20                    | Updated spelling of multiplexer to be consistent                                                      |

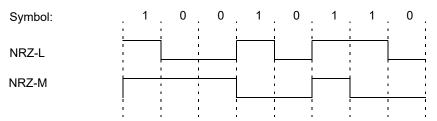

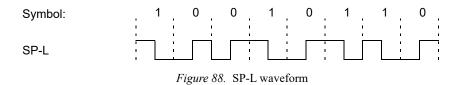

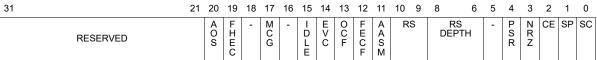

|       |            | 20.1                  | Clarification of connection between registers and BUS A mux                                           |