Status:

Available

The LEON3 processor offers robust fault tolerance and performance for space and high-reliability applications, including satellites and scientific instruments.

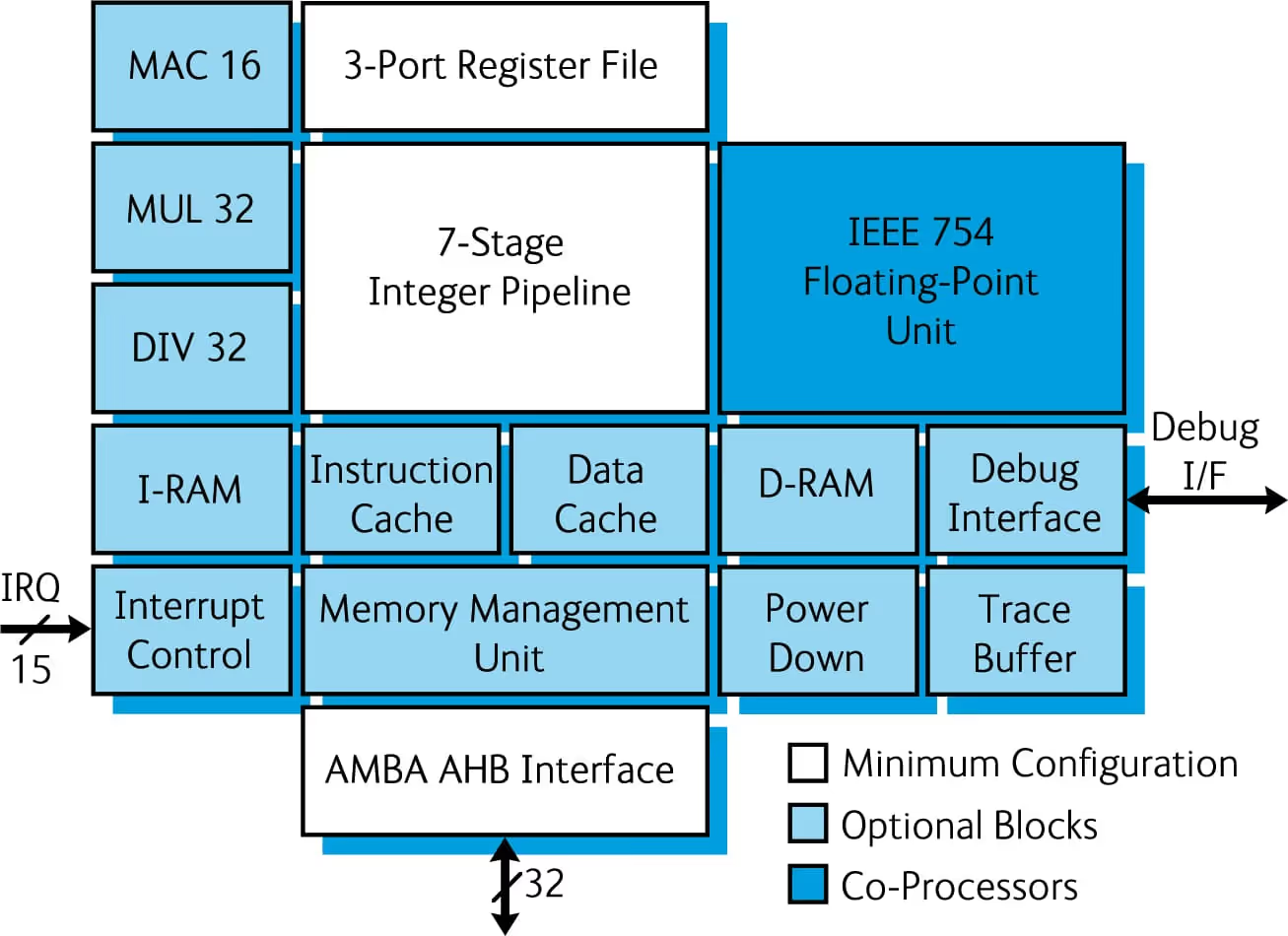

The LEON3 is a synthesisable VHDL model of a 32-bit processor compliant with the SPARC V8 architecture. The model is highly configurable and particularly suitable for system-on-a-chip (SOC) designs.

LEON3 supports both asymmetric and symmetric multiprocessing (AMP/SMP). Up to 16 CPUs can be used in a multiprocessing configuration.

LEON3 is also available in a fault-tolerant version, the LEON3FT.

LEON3 has been certified by SPARC International as being SPARC V8 conformant. The certification was completed on May 1, 2005.

File

Category

Revision

Date

Access

GRLIB IP Library

2025.2

2025-07-04

Free download

Password/

Contact us

Data sheet and user's manual

2025.2

2025-10-30

Free download

Password/

Contact us

Data sheet and user's manual

2025.2

2025-10-30

Free download

Password/

Contact us

Technical note

1.1

2016-05-27

Free download

Password/

Contact us