Status:

Development

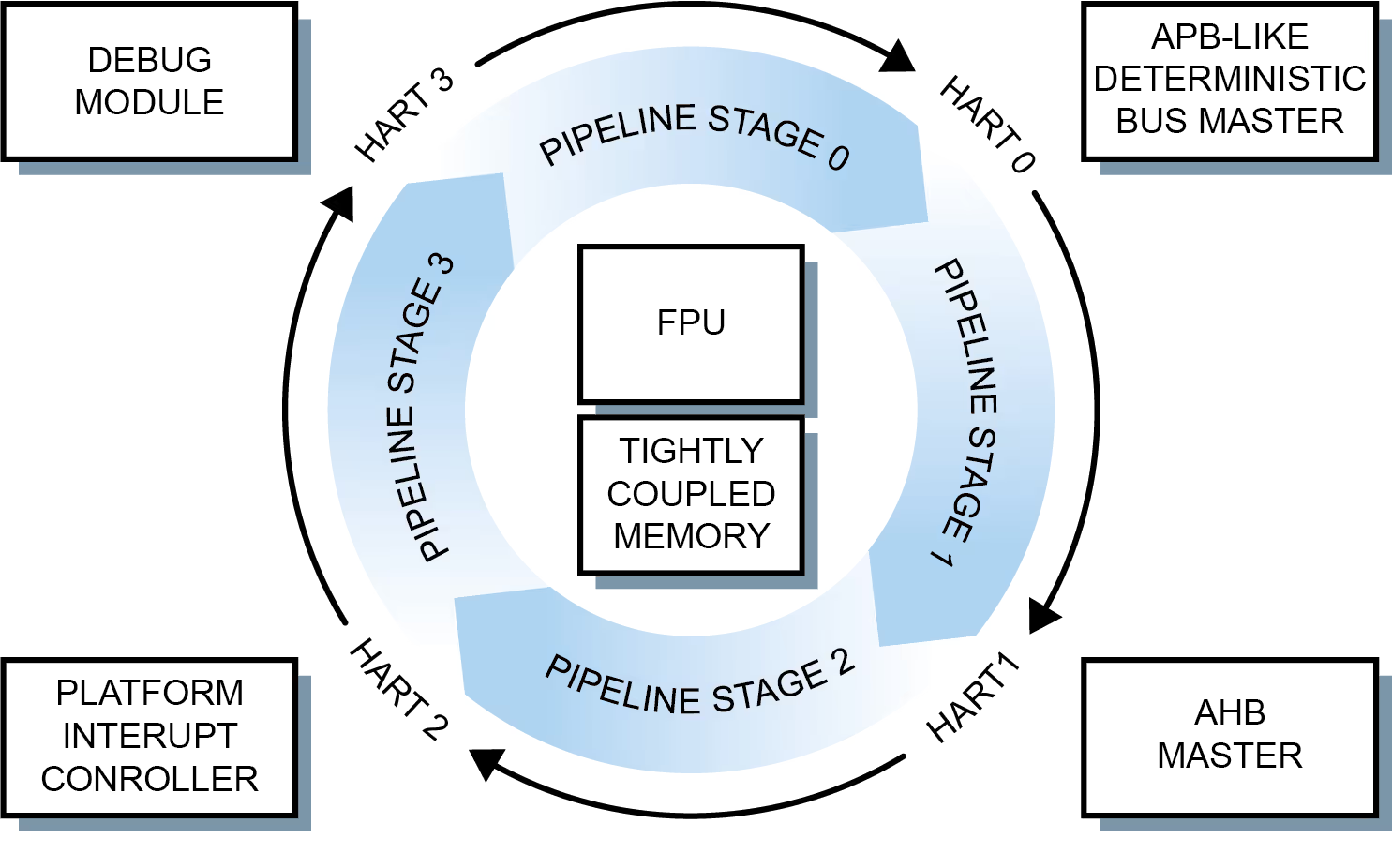

The NOEL3 is a configurable RISC-V processor IP core, described in VHDL. The architecture is designed to utilize a small area footprint and to maintain execution time predictability.

We provide example bitfiles for evaluate the NOEL3 RISC-V processor in several FPGA development boards.

See the dedicated webpage: NOEL3 examples

File

Category

Revision

Date

Access

Data sheet and user's manual

2025.2

2025-10-30

Free download

Password/

Contact us

Data sheet and user's manual

2025.2

2025-10-30

Free download

Password/

Contact us

Data sheet and user's manual

1.0

2025-12-19

Free download

Password/

Contact us