Status:

Development

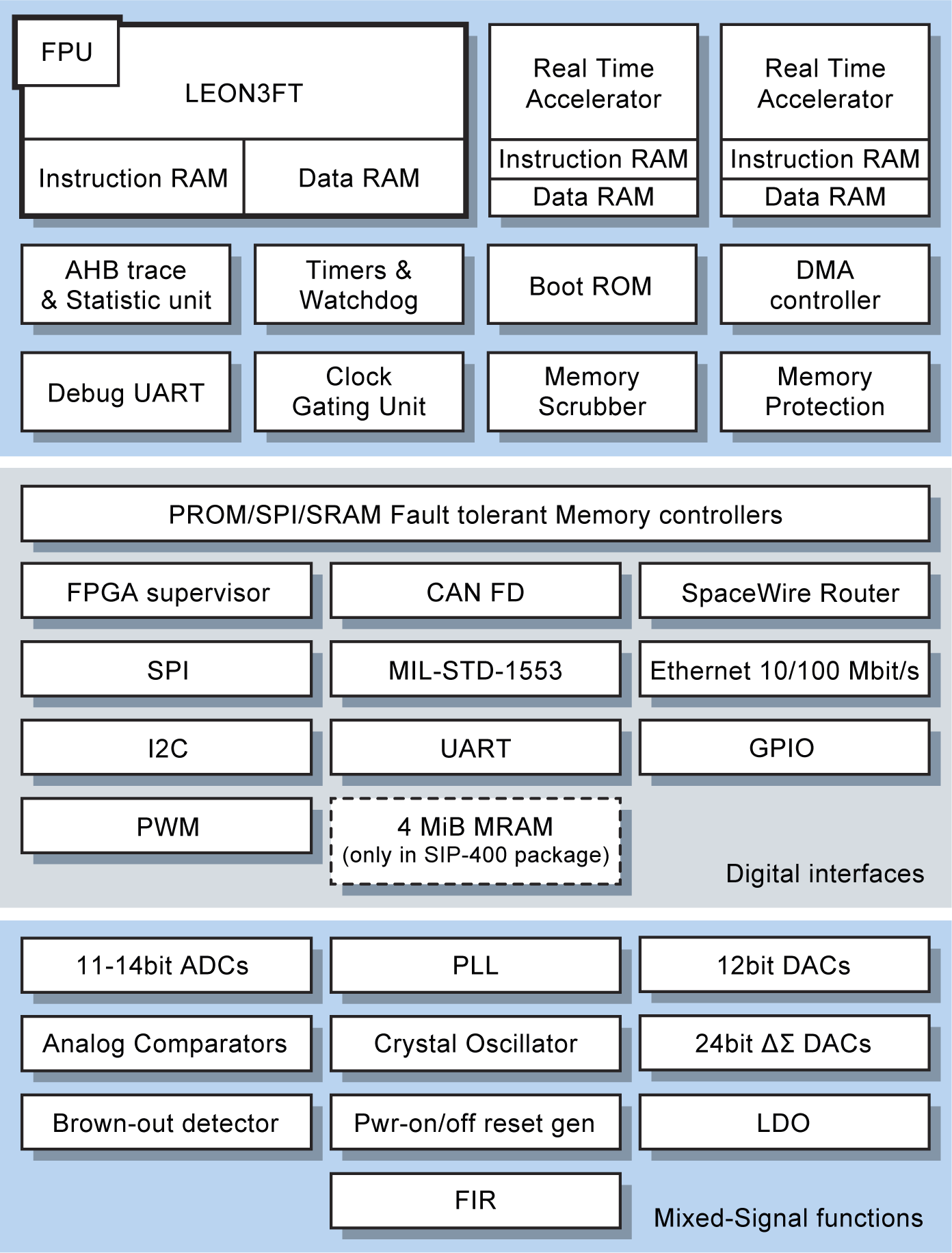

The GR716B is a radiation-hardened microcontroller featuring the fault-tolerant LEON3FT SPARC V8 processor and two Real-Time Accelerators.

This page describes a running development. All information on this page is subject to change without notice. Please click this link to sign up to receive notifications about product and documentation updates.

-------------

The GR716B is a radiation-hardened microcontroller featuring the fault-tolerant LEON3 SPARC V8 processor. Based on the GR716A design, the GR716B has been developed to provide higher computational performance and excellent communication interfaces.

The GR716B is available in three different packages:

The GR716B PBGA and SIP devices with 400-pin package have fewer pin-sharing constraints compared to GR716B devices with a 132-pin package.

Applications: DC/DC conversion

GR716B has integrated dedicated hardware to support at least 4 independent digitally-controlled DC/DC converters in peak-current control mode, or more in voltage control mode.

Applications: Motor control

The GR716B architecture supports at least 4 brushless direct current (BLDC) motors or 4 permanent magnet synchronous motors (PMSM), in PWM control mode, or 6

micro stepper motors, or a combination of DC/DC controllers and different motors. The integrated hardware support for fullbridge and half-bridge power-converter topologies can be used to control a variety of different motor types. In motor control applications, hardware support for power converters can be combined with the ability to configure ADC measurements on at least 3 analog channels with simultaneous sampling time point for optimum motor regulation.

Applications: FPGA Supervisor

The GR716B implements a FPGA configuration supervisor responsible for programming and scrubbing the FPGA configuration memory to prevent accumulation of errors. The core is compatible with the Kintex UltraScale and Virtex-5 Xilinx FPGA families and it can be set to scrub the entire FPGA configuration memory or just a smaller area. The FPGA configuration memory is accessed through the SelectMap interface. The supervisor makes use of a golden FPGA configuration file that can be stored in ROM or RAM. The GR-CPCIS-XCKU board offers a convenient platform to evaluate this capability.

Interfaces

Integrated Analog functions

Memory support

The GR716B microcontroller is currently under validation.

File

Category

Revision

Date

Access

Data sheet and user's manual

0.3

2026-02-25

Free download

Password/

Contact us

Data sheet and user's manual

0.1

2025-11-14

Free download

Password/

Contact us

Data sheet and user's manual

0.1

2025-11-14

Free download

Password/

Contact us

Application note

1.0

2024-11-25

Free download

Password/

Contact us

Application note

1.0

2024-11-25

Free download

Password/

Contact us

Technical note

1.1

2016-05-27

Free download

Password/

Contact us

Technical specification

1

2017-11-24

Free download

Password/

Contact us

Application note

1.2

2024-08-26

Free download

Password/

Contact us