Status:

Available

The LEON4 processor builds on the success of its predecessors, providing enhanced performance and efficiency for demanding space and high-reliability applications.

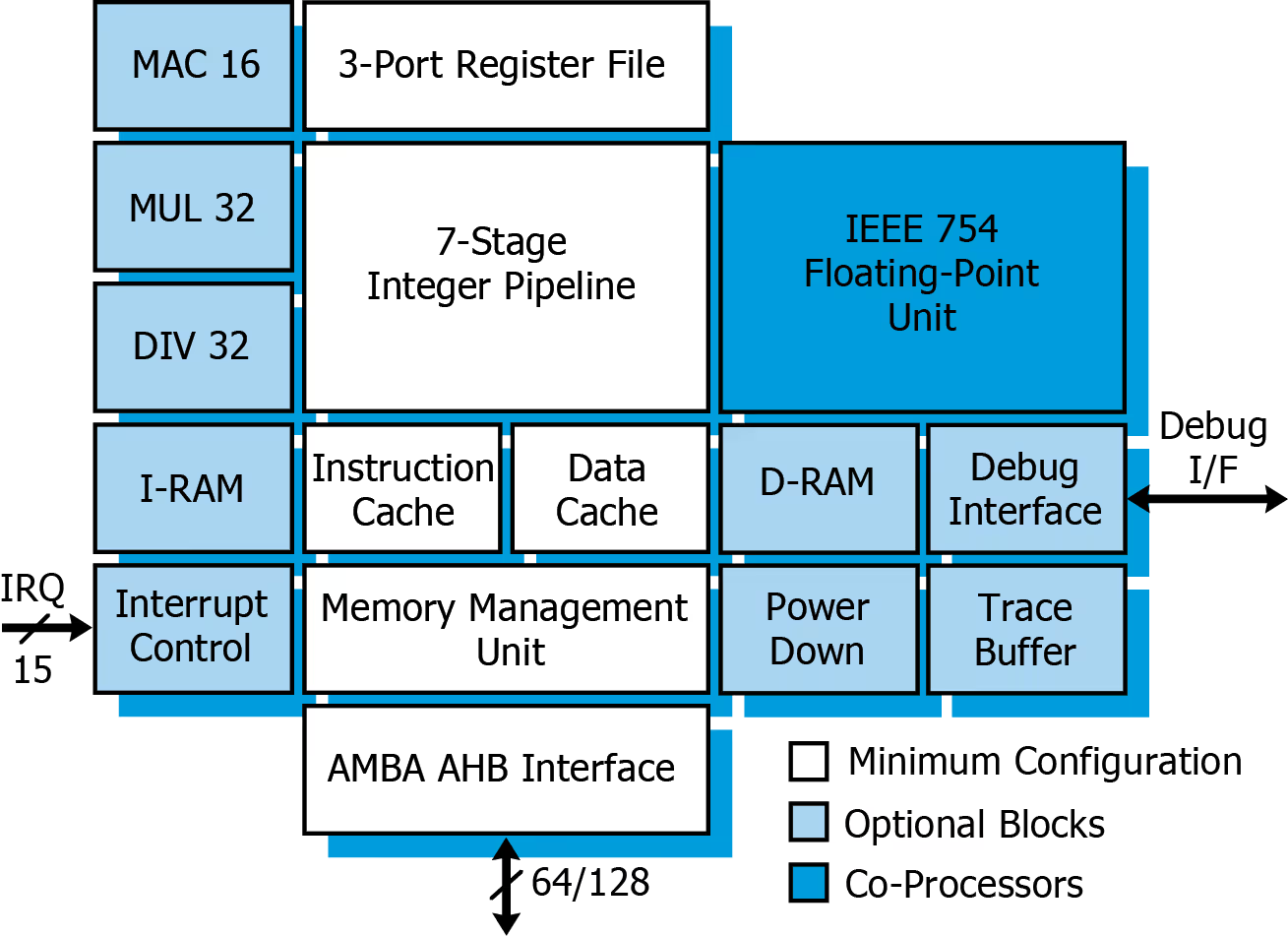

The LEON4 is a synthesizable VHDL model of a 32-bit processor compliant with the SPARC V8 architecture. The model is highly configurable, and particularly suitable for system-on-chip (SOC) designs.

The LEON4 processor can be enhanced with fault-tolerance features against SEU errors. The processor can be efficiently implemented on FPGA and ASIC technologies and uses standard synchronous memory cells for cache and register file.

The LEON4 processor is fully parameterizable through the use of VHDL generics, and does not rely on any global configuration package. It is thus possible to instantiate several processor cores in the same design with different configurations.

File

Category

Revision

Date

Access

Data sheet and user's manual

2025.2

2025-10-30

Free download

Password/

Contact us

Data sheet and user's manual

2025.2

2025-10-30

Free download

Password/

Contact us