Status:

Available

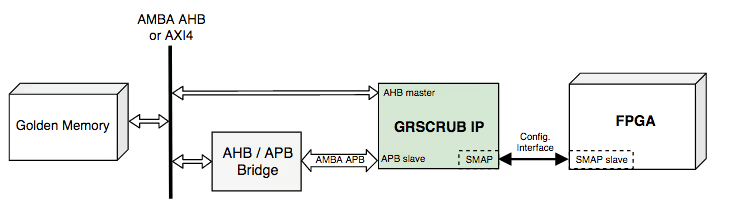

GRSCRUB is an FPGA supervisor responsible for programming and scrubbing the FPGA configuration memory to prevent the accumulation of radiation-induced errors. The GRSCRUB IP currently supports the AMD/Xilinx Kintex UltraScale and Virtex-5 FPGA families.

The GRSCRUB is an external FPGA configuration monitor that features programming and scrubbing capabilities. After the initial configuration, the GRSCRUB is self-standing, which releases the processor core to perform other tasks. The GRSCRUB is compatible with the AMD/Xilinx Kintex UltraScale and Virtex-5 FPGA families. It accesses the target FPGA configuration memory externally through the SelectMap interface. GRSCRUB is intended to be used as an external entity to the FPGA being supervised.

File

Category

Revision

Date

Access

Data sheet and user's manual

2025.2

2025-10-30

Free download

Password/

Contact us

White paper

1.0

2020-07-15

Free download

Password/

Contact us

Application note

1.0

2021-06-30

Free download

Password/

Contact us

Research paper

1.0

2022-07-03

Free download

Password/

Contact us

Application note

1.0

2020-06-12

Free download

Password/

Contact us